SoC (System on Chip,片上系统) 是采用ASIC(ApplICation Specific Integrated Circuits) 设计方法学中的新技术,以嵌入式系统为核心,以IP 复用技术为基础,集软、硬件于一体,并追求产品系统包容的集成芯片。狭意些理解,可以将它翻译为“系统集成芯片”,指在一个芯片上实现信号采集、转换、存储、处理和I/O 等功能,包含嵌入软件及整个系统的全部内容;广义些理解,可以将它翻译为“系统芯片集成”,指一种芯片设计技术,可以实现从确定系统功能开始,到软硬件划分,并完成设计的整个过程。

SoC 的设计基础是IP(Intellectual Property)复用技术。SoC 芯片需要集成一个复杂的系统,这导致了它具有比较复杂的结构,如果是从头开始完成芯片设计,显然将花费大量的人力物力。另外,现在电子产品的生命期正在不断缩短,这要求芯片的设计可以在更短的周期内完成。为了加快SoC 芯片设计的速度,人们将已有的IC 电路以模块的形式,在SoC 芯片设计中调用,从而简化芯片的设计,缩短设计时间,提高设计效率。这些可以被重复使用的IC 模块就叫做IP 模块(或者系统宏单元、芯核、虚拟器件)。IP 模块是一种预先设计好,已经过验证,具有某种确定功能的集成电路、器件或部件。它有3 种不同形式:软IP 核(soft IP core)、固IP 核(firm IP core)和硬IP 核(hard IP core)。

1.软IP

核软IP 核主要是基于IP 模块功能的描述。它在抽象的较高层次上对IP 的功能进行描述,并且已经过行为级设计优化和功能验证。它通常以HDL 文档的形式提交给用户,文档中一般包括逻辑描述、网表,以及一些可以用于测试,但不能物理实现的文件。使用软IP,用户可以综合出正确的门电路级网表,进行后续结构设计,并借助EDA 综合工具与其他外部逻辑电路结合成一体,设计出需要的器件。虽然,软IP 的灵活性大,可移植性好,但同硬IP 相比,因为它不含有任何具体的物理信息,所以如果后续设计不当,很可能导致设计失败。另外,后续的布局布线工作也将花费大量的时间。

2.硬IP

核硬IP 核主要是基于IP 模块物理结构的描述。它提供给用户的形式是电路物理结构掩模版图和全套工艺文件,是可以拿来就用的全套技术。其优点为,完成了全部的前端和后端设计,已有固定的电路布局局和具体工艺,可以确保性能,并缩短SoC 的设计时间。但因为其电路布局和工艺是固定的,同时也导致了灵活性较差,难以移植到不同的加工工艺。

3.固IP

核固IP 核主要是基于IP 模块结构的描述,可以理解为介于硬IP 和软IP 之间的IP 核。固IP 一般以门电路级网表和对应具体工艺网表的混合形式提交用户使用。以便用户根据需要进行修改,使它适合某种可实现的工艺流程。近年来电子产品的更新换代周期不断缩短,而系统芯片的复杂程度却在增长,为了缓和这一矛盾,SoC 设计普遍采用基于IP 模块的设计方法。因为IP模块是预先设计好的,并通过了验证,设计者可以把注意力集中于整个系统,而不必考虑各个模块的正确性和性能,这除了能缩短SoC 芯片设计的时间外,还能降低设计和制造成本,提高可靠性。IP 重用技术使芯片设计从以硬件为中心,逐渐转向以软件为中心,从门级的设计,转向IP 模块和IP 接口级的设计。构建一个系统是个复杂的过程,实际应用中,设计者往往到设计的后期才可以明确软件和硬件要实现的功能,系统要达到的性能等具体指标。而这些指标又实际决定了该选择哪个IP 模块。当然,不是所需要的IP 内核模块都可以从市场上买得到,为了垄断市场,一些公司开发出来的关键IP 内核模块是不愿意授权转让的。像这样的IP 内核模块就只有自己组织力量来开发了。

(1)DSM 工艺技术: 尽管这个课题已经提出相当长的时间, 但是研究的思路和方法仍然在面向逻 辑设计的思路中徘徊.也许布局规划或者时序驱动能够解决部分实际的问题,但 是随着工艺的不断进步,谁也不能保证现在的技术就能有效.

(2)IP 复用: 包括 IP 的使用和生成两个部分,IP 的使用不等同于 ASIC 设计中单元库的 使用, 它所涉及的内容覆盖了集成电路设计中很多经典的课题, 包括测试, 验证, 模拟和低功耗等等.IP 的生成也不是简单的设计抽取和整理,它所涉及的设计 思路,时序的要求和性能的要求需要我们不断的提高设计水平.

(3)软硬件协同设计: 传统的集成电路设计都是硬件设计, 少数的软件也往往是通过固化的方法在芯片中实现.但是在 SOC 设计中,不仅要面对复杂的逻辑设计,更要考虑软件, 特别是那些可以改变芯片功能的外部应用软件的设计, 尽管软件的加入增加了系 统设计的工作量,但是软件也可以减少系统的代价.如何在软件和硬件设计中取 得平衡是 SOC 设计中要考虑的一个很重要的问题.

从技术层面上看,以下几个方面推动了SoC 技术的发展:

(1) 微电子技术的不断创新和发展,大规模集成电路的集成度和工艺水平不断提高,已从亚微米(0.5 到1 微米)进入到深亚微米(小于0.5 微米),和超深亚微米(小于0.25 微米)。其特点为:工艺特征尺寸越来越小、芯片尺寸越来越大、单片上的晶体管数越来越多、时钟速度越来越快、电源电压越来越低、布线层数越来越多、I/O 引线越来越多。这使得将包括的微处理器、存储器、DSP和各种接口集成到一块芯片中成为可能。

(2) 计算机性能的大幅度提高,使很多复杂算法得以实现,为嵌入式系统辅助设计提供了物理基础。

(3) EDA(Electronic Design Automation,采用CAD 技术进行电子系统和专用集成电路设计)综合开发工具的自动化和智能化程度不断提高,为嵌入式系统设计提供了不同用途和不同级别的一体化开发集成环境。

(4) 硬件描述语言HDL(Hardware Description Language)的发展为电子系统设计提供了建立各种硬件模型的工作媒介。目前,比较流行的HDL 语言包括已成为IEEE STD1076 标准的VHDL、IEEE STD 1364 标准的Verilog HDL和Altera 公司企业标准的AHDL 等。

SoC 具有以下几方面的优势。

(1) 降低耗电量:随电子产品向小型化、便携化发展,对其省电需求将大幅提升,由于SoC 产品多采用内部讯号的传输,可以大幅降低功耗。

(2) 减少体积:数颗IC 整合为一颗SoC 后,可有效缩小电路板上占用的面积,达到重量轻、体积小的特色。

(3) 丰富系统功能:随微电子技术的发展,在相同的内部空间内,SoC 可整合更多的功能元件和组件,丰富系统功能。

(4) 提高速度:随着芯片内部信号传递距离的缩短,信号的传输效率将提升,而使产品性能有所提高。

(5) 节省成本:理论上,IP 模块的出现可以减少研发成本,降低研发时间,可适度节省成本。

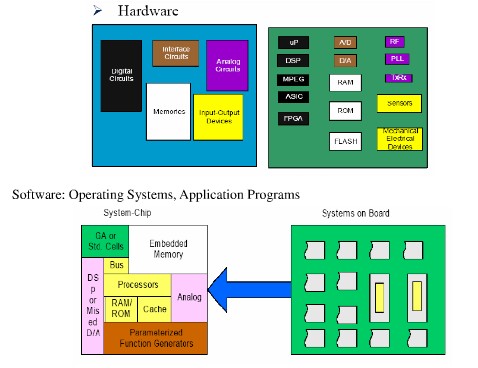

SOC 一般有三个部分:

(1)IP 核

(2)内嵌存储器

(3)集成专用的外围硬件

(1)设计理念与传统 IC 不同:SOC 把系统的处理机制,模型算法,芯片结构 各层次电路直到器件的设计紧密结合,在一个单片上完成整个系统的功能.

(2)SOC 设计以 IP 核为基础,以 HDL 为主要描述手段,借助于先进的 EDA 工具进行设计

(1)电路规模大: 设计数据管理:整个设计团队都需要同时共享设计数据,同时也使得数据量呈爆炸性增长, 设计周期长使得市场压力大,设计和验证过程更加困难更加依赖 EDA 工具

(2)更小的器件尺寸:采用短沟道设计技术使得器件行为更加复杂,更加容易具有热电子效应和氧化层穿透,更加容易受到温度,电磁辐射和供电电压环境的影响

(3)高密度集成:采用多层互连技术,高功率消耗和散热问题,芯片内部互连线决定了芯片的性能:连线延迟增加和晶体管开关速度提高,器件和连线之间的耦合效应不段增长:干扰噪声,耦合电容增加了连线延迟 (4)SOC 的集成:需要更多的板级设计工程师 IP 复用技术,新的设计和验证方法学(比如模拟电路的综合以及模拟电路的静态时序验证) SOC 设计更加的复杂(协同验证,混合信号,虚拟验证环境以及 IP 复用)

(5)低功耗设计:散热技术,便携设备的低功耗应用 VDD 降低后的低噪声容限问题 MOS 管的开启电压下降问题,更加突出的静态漏电流问题。

由于供电电压降低使得器件更容易受外界因素影响

(6)高频率设计:电感影响、连接孔耦合噪声、消耗功率多、可靠性降低、更复杂的器件模型,设计容限降低,使得数字信号看起来像模拟信号

(7)新的工艺和设计技术挑战:各种不同的器件模型、新的设计和验证方法学、需要处理前端和后端物理设计

(8)IP 复用技术:需要集成更多的 IP 工艺变化的时候需要重新定义 IP 的特性 SOC 设计者对 IP 了解甚少,调试和优化 IP 核困难

(9)验证:由于 SOC 设计中的多样性使得验证更加困难(数字验证,模拟验证,混合 信号验证,存储器验证,时序,功耗和信号完整性验证,后端版图电路仿真) 可测性设计技术

(10)封装挑战:端口数目更多的封装技术,粘接线变长将影响成品性能。

维库电子通,电子知识,一查百通!

已收录词条705078个