片上系统(System on a Chip,简称:SoC)指的是在单个芯片上集成一个完整的系统的技术,所谓完整的系统一般包括中央处理器(CPU)、存储器、以及外围电路等。

片上系统的具体定义为:在单个芯片上集成一个完整的系统,一般包括系统级芯片控制逻辑模块、微处理器/微控制器CPU内核模块、数字信号处理器DSP模块、嵌入的存储器模块、和外部进行通信的接口模块、含有ADC/DAC的模拟前端模块、电源提供和功耗管理模块,是一个具备特定功能、服务于特定市场的软件和硅集成电路的混合体,比如WLAN基带芯片、便携式多媒体芯片、DVD播放机解码芯片等。片上系统产品的成功关键在于需要在正确的时间窗口为目标用户提供令人满意的性能和价格。

片上系统技术始于20世纪90年代中期,随着半导体工艺技术的发展,IC设计者能够将愈来愈复杂的功能集成到单硅片上,SoC正是在集成电路(IC)向集成系统(IS)转变的大方向下产生的。1994年Motorola发布的FLEX-CORE系统(用来制作基于68000和PowerPC的定制微处理器)和1995年LSILogic公司为Sony公司设计的SoC,可能是基于IP(Intellectual Property)核完成SoC设计的最早报道。由于SoC可以充分利用已有的设计积累,从而显着地提高了ASIC的设计能力,因此发展非常迅速,引起了工业界和学术界的关注。

近10 年来,无论是消费类产品如电视、录像机,还是通信类产品如电话、网络设备,这些产品的核心部分都开始采用芯片作为它们的“功能中枢”,这一切都是以嵌入式系统技术得到飞速发展作为基础的。片上系统是ASIC(Application Specific Integrated Circuits)设计方法学中的新技术,是指以嵌入式系统为核心,以IP 复用技术为基础,集软、硬件于一体,并追求产品系统包容的集成芯片。狭意些理解,可以将它翻译为“系统集成芯片”,指在一个芯片上实现信号采集、转换、存储、处理和I/O 等功能,包含嵌入软件及整个系统的全部内容;广义些理解,可以将它翻译为“系统芯片集成”,指一种芯片设计技术,可以实现从确定系统功能开始,到软硬件划分,并完成设计的整个过程。

片上系统常具备以下基本特征:

1.片上系统中可以有多个MPU、DSP、MCU或其复合的IP核;

2.片上系统内嵌有系统软件或可载入的用户软件;

3.片上系统应由可设计重用的IP核组成,IP核是具有复杂系统功能、能够独立出售的VLSI模块;

4.片上系统应采用深亚微米以上的工艺技术。

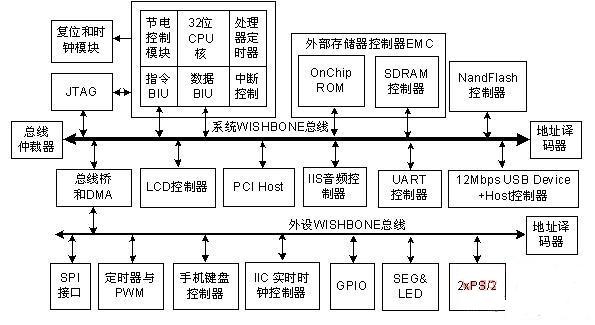

在DemoSoC中,各个模块通过一个高速的系统总线和一个低速的外设总线相连接;还包括一个32位处理器,控制所有外设协调工作。DemoSoC各个子模块描述如下:

1.32位开源处理器核OR1200,处理器核是整个SoC的核心控制单元

除CPU核外,该处理器内部还集成了定时器(用于操作系统“心跳”中断)、中断控制器、节电控制模块(电源管理模块)。该处理器是哈佛架构,指令和数据分开,分别通过指令总线接口单元(Bus Interface Unit)和数据总线接口单元连接到片上总线,这两个总线接口单元都是总线组设备。

2.NandFlash控制器

连接到NandFlash,实现到NandFlash的访问。NandFlash的存储容量非常大,是U盘的核心器件,其写入和读取过程复杂度相当,因此一般不能直接用做启动ROM,必须辅助以其他手段才能用于启动ROM。后文将详细讲述。

3.外部存储器控制EMC模块,其内部包括SDRAM控制器和OnChipROM控制器

OnChipROM用于存储处理器启动后执行的最初代码,完成整个系统最基本的初始化工作。SDRAM的单个存储单元面积小,因此SDRAM的容量大,读写速度较快,这是高性能计算机系统所需要的。SDRAM的缺点也是控制相对复杂。SDRAM与NandFlash相互配合,构成了现代高性能嵌入式系统的存储系统。嵌入式系统与PC相比较,SDRAM是内存,而NandFlash则等价于硬盘。

4.IIS音频控制器

IIS是Inter-IC Sound的简写,该接口是数字音频到音频编解码器之间的接口,用于在它们之间传送立体声音频。类似于IIS,AC97同样是另外一种音频接口标准。AC97在个人计算机系统中应用较多,而IIS更多的见诸于嵌入式系统。高等级的音频有时采用SPDIF接口。

5.12Mbps USB Device+Host控制器

该模块包括USB从设备和主设备两个部分。在嵌入式系统中,USB从设备一般用于取代串口实现更高速度的嵌入式设备与PC之间的连接,用于设备调试;而USB主设备接口则用于连接一些性能不高的USB外设,包括U盘和其他设备。在DemoSoC中,480Mbps的高速USB设备(包括主设备和从设备)可连接到PCI Host接口。

6.总线桥和DMA

总线桥的作用是将高速总线和低速总线区分开。在一般的高性能嵌入式系统中,高速总线的速度一般是低速总线的2倍、4倍、8倍可调节,而CPU的时钟频率是高速总线的1倍、2倍、4倍可调节。总线桥的个核心设计目的是节电,第二个目的是减少高速总线的容性负载,第三个目的是实现高速总线和低速总线的速率解耦,目的三是目的一的代价。DMA用于在设备之间搬运数据,从而将处理器解放出来处理更重要的任务。一般DMA放置于总线桥中,这是因为总线桥是最方便访问两个总线的位置,只有放在总线桥中,DMA才能效。

7.LCD控制器

根据是否自带显存,LCD可以分为RGB接口LCD和智能LCD。RGB接口LCD不带显存,必须依赖总线主设备上的存储器作为显存,因此,RGB接口LCD控制器模块是一个总线主设备,当显存刷新失败时将产生中断等待处理器进行处理。智能LCD自带显存,处理器只根据显示的需要对显存的特定像素寄存器和其他控制器进行简单的操作即可。考虑到显存的价格因素,智能LCD更多在低端嵌入式设备中采用,屏幕尺寸一般较小。

8.手机键盘控制器

手机键盘是4?6的小型扫描键盘。手机键盘控制器的设计要点在于键盘的防抖。

9.IIC接口模块

在DemoSoC中,IIC接口用于连接实时时钟控制器。实时时钟是许多便携式嵌入式系统必备的模块。实时时钟控制器通过IIC接口与嵌入式控制器相连接。IIC是Inter-IC Communication的缩写,其特点是管脚数只有两个。IIC已经成为许多嵌入式控制器的必备模块。

10.定时器和PWM

定时器为系统提供定时功能,如协议的超时,串口速率的自动检测等。PWM是脉冲宽度调制的缩写,典型的应用之一为控制LCD背光的亮度。PWM脉冲一般基于定时器产生。

11.JTAG模块

JTAG接口模块的用途为在线调试、跟踪、寄存器访问。一方面JTAG模块可以取代处理器访问总线上的设备;另一方面,它可以与处理器的开发接口相连接,实现端点、单步、跟踪等调试功能,这些是处理器调试所必需的。

12.SPI接口模块

SPI接口的作用为对LCD内部控制器芯片、基带芯片等进行初始化。

13.UART模块

实现RS232串口,多用于开发过程的调试,有时也用于数据输入,如全球定位系统(GPS)模块的输出就是通过串口。

14.PS/2接口模块

连接键盘和鼠标。

15.PCI Host模块

PCI Host模块实现PCI总线到片内总线的桥接功能,实现PCI主设备逻辑,通过PCI Host模块,DemoSoC可以连接到其他具有PCI接口的设备,如RTL8139C 10/100Mbps自适应以太网、ISP1561 480Mbps USB从设备等。

16.GPIO模块

GPIO模块是通用输入输出接口,可以连接键盘等慢速设备。

17.复位和时钟模块

理想的复位逻辑是异步产生,同步取消,因而必须对输入的复位信号进行处理,包括去抖动等。时钟模块将主时钟进行合成后产生不同频率的时钟信号供不同的外设使用。

(1)SoC 具有以下几方面的优势:

1.减少体积重量:数颗IC 整合为一颗SoC后,可有效缩小电路板上占用的面积,达到重量轻、体积小的特色

2.降低用电功耗:随电子产品向小型化、便携化发展,对其省电需求将大幅提升,由于SoC 产品多采用内部讯号的传输,可以大幅降低功耗。

3.提高运行速度:随着芯片内部信号传递距离的缩短,信号的传输效率将提升,而使产品性能有所提高。

4.丰富系统功能:随微电子技术的发展,在相同的内部空间内,SoC 可整合更多的功能元件和组件,丰富系统功能。

5.节省投入成本:理论上,IP模块的出现可以减少研发成本,降低研发时间,可适度节省成本。不过,在实际应用中,由于芯片结构的复杂性增强,也有可能导致测试成本增加,及生产成品率下降。虽然,使用基于IP 模块的设计方法可以简化系统设计,缩短设计时间

(2)但随着SoC 复杂性的提高和设计周期的进一步缩短,也为IP 模块的重用带来了许多问题:

1. 要将IP 模块集成到SoC 中,要求设计者完全理解复杂IP 模块的功能、接口和电气特性,如微处理器、存储器控制器、总线仲裁器等。

2. 随着系统的复杂性的提高,要得到完全吻合的时序也越来越困难。即使每个IP 模块的布局是预先定义的,但把它们集成在一起仍会产生一些不可预见的问题,如噪声,这些对系统的性能有很大的影响。IP 模块的标准化可以在一定程度上解决上述问题。过去,各个芯片设计公司、IP 厂商和EDA 公司以自己内部的规范作为设计标准,但随着SoC 设计的中心向用户端的转移,IP 模块的广泛使用,以及越来越多EDA 工具的出现,这些内部标准已经无法适应SoC 设计的需要。

从技术层面上看,以下几个方面推动了SoC 技术的发展:

1.计算机性能的大幅度提高,使很多复杂算法得以实现,为嵌入式系统辅助设计提供了物理基础。

2.微电子技术的不断创新和发展,大规模集成电路的集成度和工艺水平不断提高,已从亚微米(0.5 到1 微米)进入到深亚微米(小于0.5 微米),和超深亚微米(小于0.25 微米)。其特点为:工艺特征尺寸越来越小、芯片尺寸越来越大、单片上的晶体管数越来越多、时钟速度越来越快、电源电压越来越低、布线层数越来越多、I/O 引线越来越多。这使得将包括的微处理器、存储器、DSP和各种接口集成到一块芯片中成为可能。

3.EDA(Electronic Design Automation) 综合开发工具的自动化和智能化程度不断提高,为嵌入式系统设计提供了不同用途和不同级别的一体化开发集成环境。

4.硬件描述语言HDL(Hardware Description Language)的发展为电子系统设计提供了建立各种硬件模型的工作媒介。目前,比较流行的HDL 语言包括已成为IEEE STD1076 标准的VHDL、IEEE STD 1364 标准的Verilog HDL和Altera 公司企业标准的AHDL 等。

片上系统是与其它技术并行发展的,如绝缘硅(SOI),它可以提供增强的时钟频率,从而降低微芯片的功耗。片上系统技术通常应用于小型的,日益复杂的客户电子设备。例如,声音检测设备的片上系统是在单个芯片上为所有用户提供包括音频接收端、模数转换器(ADC)、微处理器、必要的存储器以及输入输出逻辑控制等设备。

在军舰、战车、飞机、导弹和航天器中集成电路的成本分别占到总成本的22%、24%、33%、45%和66%。随着通讯行业的迅猛发展和信息家电的迅速普及,迫使集成电路产商不断发展IC 新品种,扩大IC 规模,增强IC 性能,提高IC 的上市时间(Time to maeket),同时还需要实现品种的通用性和标准化,以利于批量生产,降低成本。据预测,SoC 销售额将从2002 年的136亿美元,增长到2007年的347亿美元,年增长率超过20%。

由于空前绝后的高效集成性能,片上系统是替代集成电路的主要解决方案。SoC 已经成为当前微电子芯片发展的必然趋势。

维库电子通,电子知识,一查百通!

已收录词条937245个