嵌入式系统源于微型计算机,是嵌入到对象体系中,实现嵌入对象智能化的计算机。由于微型计算机无法满足绝大多数对象体系嵌入式要求的体积,价位与可靠性,所以嵌入式系统迅速走上了独立发展的道路。首先是将计算机芯片化,集成为单片微型计算机,其后为满足对象体系的控制要求,单片机不断从单片微型计算机向微控制与片上系统发展。

"嵌入性"由早期的微型机时代的嵌入式计算机应用而来,专指计算嵌入到对象体系中,实现对象体系的智能控制。当嵌入式系统变成一个独立的应用产品时,可将嵌入性理解为内部嵌有微处理器或计算机。

内含计算机是对象系统智能化控制的根本保证,随着单片机向MCU、SOC发展,片内计算机外围电路、接口电路、控制单元日益增多,专用计算机系统演变成为内含微处理器的现代电子系统。与传统的电子系统相比较,现代电子系统由于内含微处理器,能实现对象系统的计算机智能化控制能力。

"专用性",是指在满足对象控制要求及环境要求下的软硬件裁剪性,嵌入式系统的软、硬件配置必须依据嵌入对象的要求,设计成专用的嵌入式应用系统。

由于各种新型微处理器的出现和应用的不断深化,嵌入式系统在后PC时代得到了空前的发展。随着时间的推移和技术的进步,在工业控制和新兴的手持式应用等领域,用户体验成为产品成功的关键因素之一,越来越多的产品需要良好的用户界面、互联功能以及较强的数据处理能力,这对嵌入式处理器硬件、软件、教学等提出了新的要求。

1 嵌入式处理器与硬件

在处理器方面,目前大量的中、低端嵌入式应用,主要使用8/16位单片机。在国内,由于历史的原因,主要是以MCS51核为主的许多不同型号单片机,主要厂商有Atmel、Philips、Winbond、宏晶等。还有一些近几年发展较快的新型单片机,如PIC、AVR、MSP430系列等。这些单片机各有特点,但从目前的发展角度来看,单片机针对特定应用领域的个性化发展愈发明显,典型的例子就是TI公司的MSP430系列16位单片机、ST公司的STM8L系列8位单片机和STM32L系列32位超低功耗单片机。

在嵌入式中的高端应用领域,像工业控制、POS机、网络设备、图像处理、手机、PDA等,目前主要使用ARM、MIPS、PowerPC、DSP等16~64位处理器,以32位处理器为主。各种类型的处理器都有其一定的应用针对性。例如,DSP对数字信号处理技术中用到的常用运算、算法做了优化设计,主要用于实时信号处理领域,如实时音视频处理、电机控制等。MIPS处理器性能很好,但功耗较大,适合于有交流电源供电的固定应用,如固定的网络设备、机顶盒等。ARM处理器性能高,功耗低,适合于用电池供电的便携、手持式设备。由于近几年便携、手持式嵌入式应用的高速发展,ARM处理器的增长速度和市场占有率也快速提升,成为目前32位应用中的主力产品。

由于嵌入式应用系统的广泛性,嵌入式系统的硬件设计涉及的知识面很广,从模拟到数字、低频到高频、小信号到大功率,以及复杂的时序逻辑设计和PCB设计,还要考虑软硬件资源的合理分配,不仅要有广而扎实的理论基础,更需要丰富的实践经验。只有对大大小小各种应用系统反复实战演练,了解新技术、新器件,使用过多种多样的处理器和模拟/数字器件,才能逐步积累,聚沙成塔,对一个新的应用系统给出快速、合理的硬件方案与设计。

2 ARM处理器的优势

对于如今大量出现的32位嵌入式应用,以笔者之见,ARM处理器的优势主要有以下几个方面。

2.1 高性能、低功耗、低价格

把ARM处理器的性能拿来和一些着名的通用处理器(如Pentium)相比是不合适的,因为他们各自针对的应用需求是不同的。Pentium处理器采用多条指令流水线的超标量结构,追求通用应用目标下的超强性能,功耗大,可以用散热器加风扇散热。ARM针对嵌入式应用,在满足性能要求的前提下,力求的功率消耗。ARM结构的优点是能兼顾到性能、功耗、代码密度、价格等几个方面,而且做得比较均衡。在性能/功耗比(MIPS/W)方面,ARM处理器具有业界的性能。基于ARM核的芯片价格也很低,目前ARM CortexM的芯片价格可低至10元人民币左右。

2.2 丰富的可选择芯片

ARM只是一个核,ARM公司自己不生产芯片,采用授权方式给半导体生产商。目前,全球几乎所有的半导体厂家都向ARM公司购买了各种ARM核,配上多种不同的控制器(如LCD控制器、SDRAM控制器、DMA控制器等)和外设、接口,生产各种基于ARM核的芯片。目前,基于ARM核的各种处理器型号有好几百种,在国内市场上,常见的有ST、TI、NXP、Atmel、Samsung、OKI、Sharp、Hynix、Crystal等厂家的芯片。用户可以根据各自的应用需求,从性能、功能等方面考察,在许多具体型号中选择最合适的芯片来设计自己的应用系统。由于ARM核采用向上兼容的指令系统,用户开发的软件可以非常方便地移植到更高的ARM平台。

2.3 广泛的第三方支持

以如今的技术,设计一个处理器并非难事,但要使这个处理器得到大家认可,并取得市场成功却是非常困难的,其中涉及许多技术与非技术的因素和环节,还包括时机、运气。因为现在许多产品的开发,不是一个简单的处理器加几百条指令、语句就可以解决的。要用到32位处理器,一般都要有编译器、高效的开发工具(仿真器及调试环境)、操作系统、协议栈等,这些东西都不是一个芯片生产商可以解决的,而需要许多第三方的支持。这就像一粒种子,需要土壤、空气、水等环境才能发芽、成长。这也是我们的一些“中国芯”该反思之处。

ARM通过近20年的培育、发展,得到了广泛的第三方合作伙伴支持。目前,除通用编译器GCC,ARM有自己的高效编译、调试环境(MDK、Keil),全球约有50家以上的实时操作系统(RTOS)软件厂商和30家以上的EDA工具制造商,还有很多高效率的实时跟踪调试工具的厂商,对ARM提供了很好的支持。用户采用ARM处理器开发产品,既可以获得广泛的支持,也便于和同行交流,加快开发进度,缩短产品的上市时间。

2.4 完整的产品线和发展规划

ARM核根据不同应用需求对处理器的性能要求,有一个从ARM7、ARM9到ARM10、ARM11,以及新定义的CortexM/R/A系列完整的产品线。前几年应用较多的主要是基于V4架构的ARM7TDMI、ARM720T、ARM920T核的一些处理器芯片,如NXP的LPC2000系列、ST的STR7/9系列、Atmel 的AT91系列和Samsung的S3C系列。近两年,ARM Cortex系列以更好的性能、更低的价格得到快速推广,典型的就是基于CortexM3的STM32系列。

ARM CortexM/R/A系列分别针对不同的应用领域。M系列主要面向传统微控制器(MCU/单片机)应用,这类应用面很广,要求处理器有丰富的外设,并且各方面比较均衡;R系列强调实时性,主要用于实时控制,如汽车引擎;A系列面向高性能、低功耗应用系统,如智能手机。选用ARM处理器进行开发,技术积累性较强,生命周期长,设计重用度高,不易被淘汰。用户在选择ARM处理器时,可以针对应用需求,从大量的ARM芯片中选用满足性能、功能要求的产品,以获得较好的性价比。

3 ARM嵌入式系统的软件

由于嵌入式系统的差异性很大,对不同的应用需求,必须选择不同的软件设计方法、开发平台和系统工具。

对于一些不需要复杂图形用户界面、通信协议和复杂文件操作(如同时打开多个文件)的应用,如果选用CortexM3核的处理器就已可以满足要求,任务数不多,任务之间的关系也不复杂,则不一定需要移植复杂的操作系统。这样一方面可以降低系统硬件开销,也可以获得更好的实时性和执行速度。不过,这样的软件开发方法需要开发人员有较好的程序设计思想,对所用器件有深入的了解,并掌握其编程控制方法。若引入一个简单的操作系统,如μC/OS,可以简化程序结构,但开发者熟悉其内核结构,并有使用经验,否则可能会需要更多的系统开发、调试时间。

如果选择了带存储器管理单元(MMU)的ARM处理器(如ARM920T、CortexA8等),这种应用系统根据应用、实时性、开发环境等因素,移植一个功能较强的操作系统一般情况下会比较合适,如Linux、WinCE,甚至新的Android等。这种系统的开发难度主要是在OS的移植以及硬件驱动程序的开发上。当这二步工作完成后,主要的软件开发工作已和在PC机上开发没有多大区别,可以按照一般的软件工程方法来进行,要注意的只是与ARM硬件平台相关的软件优化问题。

由于嵌入式系统硬件资源的有限性,嵌入式软件与其他应用软件的主要区别,在于嵌入式软件要有较高的效率,包括执行速度和存储空间,尽管这二者经常是相互矛盾的。目前一般要求更多的是速度优化。要编写出高效的ARM程序,需要开发人员熟悉ARM的体系结构,包括内核结构、指令系统、Cache与存储器结构等,还要有好的程序设计思想,以及对一些常用函数、算法的深刻理解。这个过程也是ARM系统开发从低级到的进阶之路。

目前,由于应用系统越来越复杂,嵌入式软件的移植性和重用性也得到了人们的高度重视,因为它直接影响到嵌入式软件的开发效率和质量。选择一种通用的开发环境和编程语言,使开发的嵌入式软件可以方便地移植到不同的硬件平台,是实现软件重用的基础。目前在ARM嵌入式系统开发中,ARM RealView、Keil以及IAR的EWARM是较好的开发平台,C/C++语言是应用最广泛的编程语言,并具有广泛的库函数、程序支持,在今后很长一段时间内,仍将在嵌入式系统应用领域中占重要地位。

4 嵌入式系统的教学

如今,嵌入式系统作为一个热门领域,其教学问题也颇受高校的关注。教学的主要目的是培养社会需要的人,由于嵌入式系统的广泛性、差异性,社会对从事嵌入系统开发人员的要求也有很大的不同,既需要从事简单8/16位单片机开发的人员,也需要从事ARM、DSP开发的人员;既要有从事硬件、底层软件开发的人员,也要有从事OS移植、应用软件开发的人员。由于整个大学学习时间和课程教学时数的限制,一个人显然不可能学习、掌握嵌入系统开发的各个层面。所以,各个学校首先应根据自身情况,明确定位,确定自己培养学生的社会适应面,然后再制定教学大纲,确定课程内容和实验平台。对于高职、普通高校的电类与非电类、软件学院等,都应该有不同的选择,而不是人云亦云,一哄而上。

就目前的发展看,由于ARM等32位处理器应用渐成主流,开发工具已较完善、成熟,对于普通高校计算机学科的嵌入式系统教学,笔者认为可以定位在以32位嵌入式系统开发为主,重点是嵌入式系统的软硬件结构、嵌入式OS的知识,以及嵌入式软件设计(包括优化)。课程主体内容基本与硬件平台(处理器型号)无关,实验可以采用基于ARM核的不同厂家处理器的实验平台。主要考虑以下几点:

①在32位嵌入式系统开发上,软件开发人员的需求比硬件开发人员要多得多(尽管目前硬件开发人员较难找,但这应该是电子等培养的)。一般在一个从事嵌入式应用系统开发的公司中,软硬件人员的比例不会小于10:1。由于学习时间有限,教学重点应该偏软件。

②现代社会强调分工、合作,以求得整体利益的化。对个人的要求首先是专才,能把局部工作做精、做好。通才是需要的,但数量会比专才少得多,而且通才是练出来的,不是教出来的。今后的大学是大众教育,教学只能面向大众需求。在相关的研究生阶段,对一些有基础、有兴趣的学生,可以进行一些系统级硬件、底层软件的开发实践,同时也可满足社会对高层次嵌入式人才的需要。

③以此为主,可以再开设2门选修课。向下为“单片机原理与应用”,此课程以实践为主,让有兴趣的学生可以自己设计、制作一些单片机应用系统,同时也锻炼了硬件动手能力。向上为“数字信号处理(DSP)”,让那些数学基础较好、对实时信号处理有兴趣的学生有用武之地(现在这样的学生很难得)。

另外,由于应用日趋复杂,而教学时间有限,一个本科生在校期间不可能深入学习嵌入式系统的很多细节,嵌入式教学应采用自上而下的教学方法。一开始不必花很多时间讲解处理器内核架构/指令系统,只要知道各种内核的基本特点即可,重点学习、掌握处理器、外设的编程结构(即编程者角度看到的编程模型结构,非具体物理实现结构)。真实的应用、研究设计都是从粗粒度向细粒度进阶的,是一个自顶向下的过程,首先要重视的是系统架构和各个抽象层。1000行的C程序,编译后生成的目标代码只有10 KB左右,试想现在的MCU Flash动辄几百KB,为什么?一个目标代码几百KB的C程序,一般不是完全由个人写出来的,而都会使用一些第三方的库函数、中间件等。硬件也一样,现在很多硬件系统都会使用一些模块(Module),尽管这些模块看上去还是一个芯片,但实际上已经是一个SiP模块,如WiFi模块。所以,在了解基本嵌入式系统结构的基础上,本科阶段要更多地学习各种系统、模块、外设、协议、库函数的“边界(Interface)”,能够搭建一个简单系统(How to do),今后在工作、或研究生阶段进一步去做好一个系统(How to do better)。

5结语

嵌入式系统作为一种特殊的计算机应用系统,在任何时期都有相对的高、中、低端应用,即使在今后,没有OS支持的4位或8位单片机的嵌入式应用仍有大量需求,但趋势是系统化、复杂化。这既是嵌入式系统的特点--广泛性、差异性和不可垄断性,也是广大嵌入系统研发人员的生存与发展空间。ARM处理器在便携、手持式设备以及工业控制等应用领域,在今后相当长的时间内是一个很好的选择。当然,没有一种型号的处理器是可以覆盖所有应用的,也不是搬上一个嵌入式OS,就可以很好地解决软件问题的。深入了解各种器件特性,选择最合适的处理器、外围器件、操作系统和软件库,尽可能地优化软件设计,最贴切地满足应用需求,以获得的系统性价比,是嵌入式系统设计开发的精髓。

嵌入式系统是将应用程序和操作系统与计算机硬件集成在一起的系统。这种系统具有软件代码小、高度自动化、响应速度快等特点,特别适合于要求实时的和多任务的体系。嵌入式设备是指应用了嵌入式系统的计算机设备。从某种意义上来讲确实是大型计算设备的微缩。这肯定多少会带来相对性能上的减弱,但正是体积的微缩带给人们无法比拟的方便。

1 嵌入式处理器技术

嵌入式系统的核心是嵌入式微处理器。嵌入式处理器是用于在计算机之外的设备中提供添加的功能性的计算机芯片,它经常用于控制和监控领域。

一些嵌入式处理器是桌面市场传下来的东西,对于今天的PC已经过时,但对于处理功能要求较低的任务却绰绰有余。过去驱动TRS-80、AppleII和Commodore64这类早期PC的Z80和6502处理器现在仍是非常畅销的产品。老式的处理器没有淡出江湖,它们只是变为嵌入式了。因此,嵌入式微处理器市场异乎寻常地广阔。在PC市场的任何时刻,最快和最慢的微处理器之间性能比最多只有约3:1。与此相比,仅就32位嵌入式微处理器来说,这个比例为500:1。如果在4位和8位嵌入式处理器中进行比较的话,则为几千比1。随着这类处理器体积越来越小,价格越来越便宜,功能越来越强大,它们将进入到更多的设备和产品中。

嵌入式系统的广泛应用正是由于嵌入式微处理器具备以下4个特点:

①对实时多任务有很强的支持能力,能完成多任务并且中断响应时间较短,从而使内部的代码和实时内核的执行时间减少到限度。

②具有功能很强的存储区保护功能。这是由于嵌入式系统的软件结构已模块化,而为了避免在软件模块之间出现错误的交叉作用,需要设计强大的存储区保护功能。同时,这也有利于软件诊断。

③可扩展的处理器结构,能迅速地开发出满足应用的高性能嵌入式微处理器。

④嵌入式微处理器必须功耗很低,尤其是用于便携式的无线及移动的计算和通信设备中靠电池供电的嵌入式系统更是如此,如要求功耗为mW甚至μW级。

1.1 嵌入式处理器的种类

1.1.1 嵌入式微处理器(EMPU)

嵌入式微处理器的基础是通用计算机中的CPU。在应用中,将微处理器装配在专门设计的电路板上,只保留和嵌入式应用有关的母板功能,这样可以大幅度减小系统体积和功耗。为了满足嵌入式应用的特殊要求,嵌入式微处理器虽然在功能上和标准微处理器基本是一样的,但在工作温度、抗电磁干扰、可靠性等方面一般都作了各种增强。

和工业控制计算机相比,嵌入式微处理器具有体积小、重量轻、成本低、可靠性高的优点,但是在电路板上必须包括ROM、RAM、总线接口、各种外设等器件,从而降低了系统的可靠性,技术保密性也较差。嵌入式微处理器及其存储器、总线、外设等安装在1块电路板上,称为单板计算机,如STD-BUS、PC104等。近年来,德国、日本的一些公司又开发出了“火柴盒”式名片大小的嵌入式计算机系列OEM产品。

嵌入式微处理器目前主要有Am186/88、386EX、SC400、Power PC、68000、MIPS、ARM系列等。

1.1.2 嵌入式微控制器(MCU)

嵌入式微控制器又称单片机,顾名思义,就是将整个计算机系统集成到1块芯片中。嵌入式微控制器一般以某一种微处理器内核为核心,芯片内部集成ROM/EPROM、RAM、总线、总线逻辑、定时器/计数器、WatchDog、I/O、串行口、脉宽调制输出、A/D、D/A、Flash、EEPR-OM等各种必要功能和外设。为适应不同的应用需求,一般一个系列的单片机具有多种衍生产品,每种衍生产品的处理器内核都是一样的,不同的是存储器和外设的配置及封装。这样可以使单片机限度地和应用需求相匹配,功能不多不少,从而减少功耗和成本。

和嵌入式微处理器相比,微控制器的特点是单片化——体积大大减小,从而使功耗和成本下降,可靠性提高。微控制器是目前嵌入式系统工业的主流。微控制器的片上外设资源一般比较丰富,适合于控制,因此称微控制器。

嵌入式微控制器目前的品种和数量最多,比较有代表性的通用系列包括8051、P51XA、MCS-251、MCS-96/196/296、C166/167、MC68HC 05/11/12/16、68300等。另外还有许多半通用系列,如支持USB接口的MCU8XC930/931、C54O、C541;支持I2C、CAN-Bus、LCD及众多专用MCU和兼容系列。目前MCU占嵌入式系统约70%的市场份额。特别值得注意的是,近年来提供X86微处理器的着名厂商AMD公司将Aml86CC/CH /CU等嵌入式处理器称为Microcontroller,Motorola公司把以Power PC为基础的PPC505和PPC555亦列入单片机行列,TI公司亦将其TMS320C-2XXX系列DSP作为MCU进行推广。

1.1.3 嵌入式DSP处理器(EDSP)

DSP处理器对系统结构和指令进行了特殊设计,使其适合于执行DSP算法,编译效率较高,指令执行速度也较高。在数字滤波、FFT、谱分析等方面,DSP算法正在大量进入嵌入式领域。DSP应用正在从通用单片机中以普通指令实现DSP功能,过渡到采用嵌入式DSP处理器。嵌入式DSP处理器有2个发展来源:一是DSP处理器经过单片化、EMC改造、增加片上外设,成为嵌入式DSP处理器,TI公司的TMS320C2000/C5000等属于此范畴;二是在通用单片机或SoC中增加I)SP协处理器,例如Intel公司的MCS-296和Siemens公司的TriCore。推动嵌入式DSP处理器发展的另一个因素是嵌入式系统的智能化,例如各种带有智能逻辑的消费类产品、生物信息识别终端、带有加解密算法的键盘、ADSL接入、实时语音压解系统、虚拟现实显示等。这类智能化算法一般都运算量较大,特别是向量运算、指针线性寻址等较多,而这些正是DSP处理器的长处所在。

嵌入式DSP处理器比较有代表性的产品是TI公司的TMS320系列和Motorola公司的DSP56000系列。TMS320系列处理器包括用于控制的C2000系列、移动通信的C5000系列,以及性能更高的C6000和C8000系列。DSP56000目前已经发展成为DSP56000、DSP56100、DSP56200和DSP56300等几个不同系列的处理器。另外Philips公司也推出了基于可重构嵌入式DSP结构低成本、低功耗技术制造的R.E.A.L DSP处理器,特点是具备双Harvard结构和双乘/累加单元,应用目标是消费类产品。

1.1.4 嵌入式片上系统(SoC)

随着EDI的推广和VLSI设计的普及化,及半导体工艺的迅速发展,在1个硅片上实现更为复杂系统的时代已来临,这就是SoC。各种通用处理器内核将作为SoC设计公司的标准库,和许多其他嵌入式系统外设一样,成为VLSI设计中的标准器件,用标准的VHDL等语言描述,存储在器件库中。用户只需定义整个应用系统,仿真通过后就可以将设计图交给半导体工厂制作样品。这样除个别无法集成的器件以外,整个嵌入式系统大部分可集成到1块或几块芯片中去,应用系统电路板将变得很简洁,对于减小体积和功耗、提高可靠性非常有利。

SoC可以分为通用和专用2类。通用系列包括Siemens公司的TriCore、Motorola公司的M-Core、某些ARM系列器件、Echelon公司和Motoro-la公司联合研制的Neuron芯片等。专用SoC一般专用于某个或某类系统中,不为一般用户所知。

1. 2 嵌入式处理器分类的变迁

国际上公认的通用嵌入式处理器有3大类:MCU、DSP和MPU(Micro-Processor Unit)。TI公司曾把处理器比作汽车:DSP是跑车,追求的是速度;MPU是轿车,追求的是经济性与速度的折中;MCU是满足特殊用途的车。

现在,随着对处理速度的要求越来越高,同时处理的数据更加复杂,出现了双核与多核处理器,通常为DSP+RISC芯核,如Infineon公司的TriCore(CISC+RISC+DSP)、Philips公司的Trimedia。随着一些大量应用市场的崛起,又出现了一些新名词,例如用于网络、通信设备的通信处理器(2000年左右兴起),数码相机、数码录像机等视频、音频流所需的媒体处理器(2003年兴起),智能手机上的应用处理器(2004年兴起)。

由于一些处理器不仅要有速度,还要有控制功能,又出现了DSP与MCU的结合品,主攻电机控制市场。如Freescale公司的DSP利用了其在MCU控制方面的技术;Microehip公司2004年2月也推出了这种产品,称为DSC(Digital Signal Controller)。

为了满足多芯核与SoC设计的需要,还有一些厂家专门供应处理器芯核的IP,芯核主要有16位、32位、64位,有软核与硬核。多芯核市场发展空间广阔,在美国Electronic Summit 2004上,做64位RISC IP的Tensilica公司总裁Chris Rowen博士说,未来10年,1块芯片中需要上千个处理器芯核,每秒要完成1012次运算。

2 嵌入式处理器芯片的开发

2.1 一般开发过程

尽管有几千种现成的芯片可供选择,但是许多设计者需要与众不同的特性。因此,他们开发自己的嵌入式芯片,即所谓的专用集成电路。

设计人员开始时需要从一家公司取得嵌入式微处理器的内核的授权,然后添加他自已应用特有的特性。例如,对于数字照相机处理器来说,他可能为这种电荷耦合设备的芯片添加1个控制器。又比如,对于具有Internet功能的家电处理器来说,可以添加1个Ethernet接口。设计者然后将他的设计交给“铸造厂”,即一家拥有“工厂”(芯片制造厂)的公司,并将部分制造量出售给其他公司。主要的制造厂有United Microelectronics公司、TSMC公司和IBM Microelectronics公司。

对于一些设计者来说,甚至这种灵活性还不够用。他们可以找到某些公司,这些公司拥有可高度定制嵌入式微处理器内核的许可证。利用这类内核,可以开发出用于特殊目的的新机器级指令。对于数字相机处理器而言,1条提高JPEG图像压缩率的指令具有很高的价值。对于MP3音乐播放器来说,1条加速音频解压缩率的指令具有同样的用处。然后,定制的设计交给“铸造厂”进行生产。

和通用计算机不同,嵌入式系统的硬件和软件都必须高效率地设计,量体裁衣,去除冗余,力争在同样的硅片面积上实现更高的性能,这样才能在具体应用对处理器的选择面前更具有竞争力。嵌入式处理器要针对用户的具体需求,对芯片配置进行裁剪和添加才能达到理想的性能;但同时还受用户订货量的制约。因此不同的处理器面向的用户是不一样的,可能是一般用户、行业用户或单一用户。

嵌入式处理器的发展也体现出稳定性,1个体系一般要存在8~lO年的时间。1个体系结构及其相关的片上外设、开发工具、库函数、嵌入式应用产品是一套复杂的知识系统,用户和半导体厂商都不会轻易地放弃1种处理器。

2.2 嵌入式系统的开发工具

嵌入式处理器是一个复杂的高技术系统,要在短时间内掌握并开发出所有功能是很不容易的,而市场竞争要求产品能够快速上市,这一矛盾要求嵌入式处理器能够有容易掌握和使用的开发工具平台,提高用户和程序员的时间一投入回报率。面对成百上千种处理器,选择是一个问题,学习掌握处理器结构及其应用更需要时间,因此以开发工具和技术咨询为基础的整体解决方案是迫切需要的。好的开发工具除能够开发出处理器的全部功能以外,还应当对用户是友好的。

嵌入式系统开发工具平台主要包括以下几类。

2.2.1 实时在线仿真系统

在计算机辅助设计非常发达的今天,实时在线仿真系统(InCircuit Emulator,ICE)仍是进行嵌入式应用系统调试最有效的开发工具。 ICE首先可以通过实际执行,对应用程序进行原理性检验,排除人难以发现的设计逻辑错误。ICE的另一个主要功能是在应用系统中仿真微控制器的实时执行,发现和排除由于硬件干扰等引起的异常执行行为。此外,的ICE带有完善的跟踪功能,可以将应用系统的实际状态变化、微控制器对状态变化的反应、以及应用系统对控制的响应等以一种录像的方式连续记录下来,以供分析,在分析中优化控制过程。很多机电系统难以建立精确有效的数字模型,或是建立模型需要大量人力,这时采用ICE的跟踪功能对系统进行记录和分析是一个快而有效的方法。

ICE不仅是软硬件排错工具,同时也是提高和优化系统性能指标的工具。ICE工具(如美国Nohau公司的产品)可根据用户投资裁减功能,亦可根据需要选择配置各种档次的实时逻辑跟踪器(Trace)、实时映像存储器(Shadow RAM)及程序效率实时分析功能(PPA)。

2.2.2 语言编译器

C语言作为一种通用的语言,大幅度提高了嵌入式系统工程的工作效率,充分发挥出嵌入式处理器日益提高的性能,缩短产品进入市场时间。另外,C语言便于移植和修改,使产品的升级和继承更迅速。更重要的是,采用C语言编写的程序易于在不同的开发者之间进行交流,从而促进了嵌入式系统开发的产业化。

区别于一般计算机中的C语言编译器,嵌入式系统中的C语言编译器要专门进行优化,以提高编译效率。的嵌入式系统C编译器代码长度和执行时间仅比以汇编语言编写的同样功能程序长5%~20%。编译效率的不同,是区别嵌入式系统C编译器性能差别的重要根据之一。而C编译器残余的5%~10%效率差别,完全可以由现代微控制器的高速度、大存储器空间以及产品提前进入市场来弥补。

新型的微控制器指令速度不断提高,存储器空间也相应加大,已经达到甚至超过了目前的通用计算机中的微处理器,为嵌入式系统工程采用过去一直不敢问津的C++语言创造了条件。C++语言强大的类、继承等功能更便于实现复杂的程序功能。但是C++语言为了支持复杂的语法,在代码生成效率方面不免有所下降。为此,1995年初在日本成立的Embedded C++技术委员会经过几年的研究,针对嵌入式应用制订了减小代码尺寸的EC++标准。EC++保留了C++的主要优点,提供对C++的向上兼容性,并满足嵌入式系统设计的一些特殊要求。在嵌入式语言编译器方面处于地位的Tasking公司,是EC++技术委员会成员之一,也是推出EC++产品的公司。

C/C++/EC++引入嵌入式系统,使得嵌入式开发和个人计算机、小型机等在开发上的差别正在逐渐消除,软件工程中的很多经验、方法乃至库函数可以移植到嵌入式系统。在嵌入式开发中采用语言,还使得硬件开发和软件开发可以分工,从事嵌入式软件开发不再必须精通系统硬件和相应的指令集汇编。

另一种语言Java的发展则具有戏剧性。Java本来是为设备独立的嵌入式系统设计、为了提高程序继承性的语言,但是目前基于Java的嵌入式开发工具代码生成长度要比嵌入式C编译工具长10倍以上。因此EC++很可能在未来的一段时间内仍是嵌入式系统的主流。

2.2.3 源程序模拟器

源程序模拟器是在广泛使用的、人机接口完备的工作平台上,如小型机和PC,通过软件手段模拟执行某种嵌入式处理器内核编写的源程序的测试工具。简单的模拟器可以通过指令解释方式逐条执行源程序,分配虚拟存储空间和外设,供程序员检查;的模拟器可以利用计算机的外部接口模拟出处理器的I/O电气信号。不同档次和功能模拟器工具价格差距巨大。模拟器软件独立于处理器硬件,一般与编译器集成在同一个环境中,是一种有效的源程序检验和测试工具。但值得注意的是,模拟器毕竟是以一种处理器模拟另一种处理器的运行,在指令执行时间、中断响应、定时器等方面很可能与实际处理器有较大差别。另外,它无法和ICE一样,仿真嵌入式系统在应用系统中的实际执行情况。

结语

嵌入式系统是将计算机直接嵌入到应用系统中,是信息技术的最终产品。嵌入式系统的核心就是嵌入式处理器。嵌入式系统是信息产业走向21世纪知识经济时代的最重要的经济增长点之一,是一个不可垄断的工业,对中国的信息产业来说充满了机遇和挑战。世界是多样化的,尤其是已经进入后PC时代——无所不在的计算(nomadic computing)将使嵌入式处理器遍及人们能够想象得到的各个角落,因此,每种处理器都有存在的理由,都有可伸展的方向。这一点应特别引起中国信息产业界的关注。

对于电池供电的便携设备而言,除了需要突破处理能力的限制外,便携式系统电源的性能也需要不断改进。本文探讨便携嵌入式系统电源设计的注意事项以及设计中应遵循的准则。这些原则对任何具有强大功能且必须以电池供电的便携嵌入式系统电源设计都是有帮助的。根据本文描述的构造模块,读者可以为特定设计选择合适的器件以及设计策略。

电源管理单元

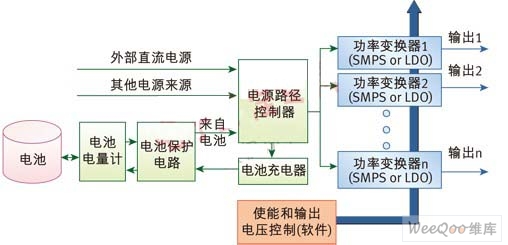

为电源电路规定具体的功能和架构模块并非微不足道,这些工作直接影响到电池供电系统的工作时间。电源系统架构会因嵌入式产品和应用领域的不同而各异。下图是典型便携嵌入式系统中的电源方案。

下面我们分别定义图中每个组成部分的要求。假设该产品由电池组或外接电源供电。电源路径控制器的功能是当有多个电源时,负责切换至合适的电源。在某些设计中可能需要考虑包括新兴的USB和以太网供电(PoE)等供电方式。

电池保护电路保护电池免受过压、欠压、过热、过流及其它异常状况的损坏;专门的电池充电电路应在一旦有其它供电来源的情况就对电池进行充电;电量计电路连续监测电池电量状况,并为用户和电源管理软件提供电池状态信息。

系统可能需要多个DC-DC功率变换器。例如开关电源(SMPS)、LDO稳压器、电荷泵等。这些不同的变换器用于产品设计内所有可能的输入电源和所需的不同电压。

数字接口或硬件按钮控制器负责开启和关闭系统——有时也称软启动。在一些最近推出的功率变换器中,数字接口也可被用来微调各种变换器产生的输出电压。在具有功耗意识的电源设计中,这种微调是必需的。

高效电源的标准

在嵌入式应用中,电源效率并不限于传统的系统输出功率与系统输入功率之比这样一个定义。在嵌入式系统,高效电源方案应满足以下标准:1. 采用电池供电时,设备可长时间工作;2. 延长电池寿命(充放电次数);3. 限制元器件和电池本身的温升;4. 提供集成软件智能,以使效率化。

事实上,没有单一的指导方针可以化电源方案的效率。不过,设计人员在开发电源系统时会考虑以下几点:电池寿命(充放电次数)取决于电池的充电特性;对锂离子电池来说,制造商通常建议遵循充电电流(恒流模式)和终止/预充电电流值。当设计充电器电路时,必须严格遵守这些规范。

电池管理

对于消费类电子产品,电池保护必须被视为基本特性,因为它与用户的人身安全息息相关。必须采取充分的措施检测电池的过压、欠压和温度;必须选用诸如温变电阻等合适的器件来确保无论在任何异常条件下,都能自动限制电流的大小;必须使用电量计。除了正常电量检测功能外,它还能确保电池安全。大部分电量计安装于电池上,可用于检测电池温度、放电电流等。

对于电源路径控制器,一个经常被忽略的问题是:当从一个电源切换到另一个时,无论时间多短,都不能在两者间形成回路。这可能需要额外的反向连接二极管或开关。同样,当采用其中一个电源供电时,该电源的电压不应通到另一个电源的输入端。

由于存在很多可用的功率变换器拓扑结构,所以正确选择电源变换器并非易事。一般来说,在需求高效率和大输出电流的场合,必须避免使用线性稳压器。

在采用开关电源的场合,设计人员应确保采用适当的拓扑(降压、升压、降压-升压,电荷泵,SEPIC等),以保证即使在电池电压下降到工作值的情况下,电源也能维持期望的输出电压,这有助于延长设备的工作时间。

对于降压变换器而言,同步变换器通常具有比异步变换器更高的效率。不过,这种架构选择在很大程度上取决于该变换器工作状态下所需的输出电流以及占空比。因此,采用同步变换器所带来的少许效率提升并不足以弥补所增加的成本。

用于滤除开关电源输出纹波的电感种类的不同通常会对变换器效率有不同影响。在各种电感选择中,低直流阻抗及在工作频率下具有低磁损耗的电感是。

热设计应与电气设计须夷不离。各个IC或无源器件的封装必须要能处理其正常工作状态下的发热问题。许多芯片制造商建议采用带过孔的热焊盘,并在PCB上采用大焊盘来更好地散热。紧凑型嵌入式产品通常没有添加风扇的空间,但必须考虑到PCB上的通风通道以及足够的散热措施。

本文小结

电源设计往往被当作纯粹的硬件设计。但是,为了得到高效的电源方案,设计人员需要为电源电路增加软件智能。软件控制的一些基本功能包括,检测由电源路径开关选择的是哪种电源;在电池供电时,对不需要的电路减少供电电流。

更精妙的电源管理软件还会包括其它参量,例如:系统运行的应用种类、外设要求、最慢时钟频率以及运行此应用所需的电压,并据此相应地控制电源输出、时钟发生器和接口IC的状态。

遵循上述经验规则可以显着提高便携式设备的电源性能。例如,一款典型的30W多输出电源方案的整体效率可高达85到90%。目前已多家集成电路制造商可提供一系列高集成度IC,具备上述各种功能。根据不同电源要求,一些应用可能需要单芯片方案,而另一些则可能采用分立模块。毕竟,在竞争激烈的嵌入式产品市场,电池寿命和设备工作时间是影响买方选择的关键因素。

图:典型便携嵌入式系统的电源管理方案。

以用各种微处理器代替通用计算机的CPU,实现既定功能并驱动显示系统以方便人机交流。早期的单片机由于低时钟频率(小于5 MHz)和低I/O口数量的限制,一般只驱动像素比较少(5 000像素以内)的液晶显示器[1-2]。近年来随着制作工艺的发展和设计结构的优化[3],单片机的时钟频率和I/O口的数量都得到了很大提高,低耗能低电压单片机不断出现[4],新调试技术使开发过程效率更高[5],驱动几千像素的液晶显示器早已出现。然而,更友好的人机界面需要更高分辨率的液晶显示器。考察目前流行的液晶显示器驱动方式可以看到,无论使用何种单片机或作为嵌入式系统的微处理器,都会被液晶显示器的驱动控制部分占据大量资源,这就给单片机的性能带来了巨大的挑战。例如三星某显示器模组,分辨率为800×480,输入时钟要求为32.24 MHz~48 MHz,这样的要求使得单片机力不从心。本文研究并开发一种面向嵌入式系统的通用显示器。它以类似于通用计算机的显存存储图像数据,以FPGA控制并读/写显存中的数据,控制液晶屏的驱动。嵌入式微处理器仅需要在改变图像时输出数据,这样,其他时间便可全部空出,用于控制其所在的自动化系统。

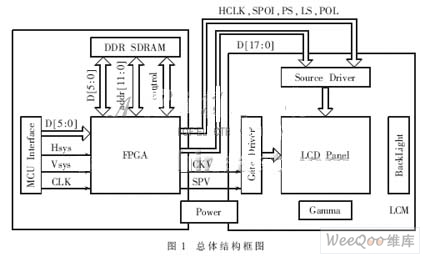

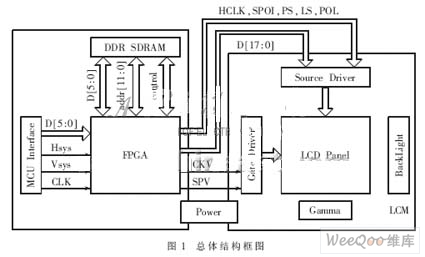

1 系统构架

由于DDR SDRAM(83 MHz~167 MHz)和液晶显示器(32.24 MHz~48 MHz)之间的时钟周期不匹配,FPGA在设计中主要起控制协调作用。系统总体构架框如图1, 分为以FPGA为中心的控制模块和液晶显示模块两部分。

FPGA控制模块部分主要负责接收来自单片机的图像数据D[5:0]和控制信号Hsys(行同步信号)、Vsys(场同步信号)和随路传输的输出图像数据的时钟信号CLK(50 MHz以下)。为了节省单片机内部的时钟资源和输出口的数量,对于18 bit彩色显示的LCM,FPGA连接单片机的图像数据输入口可设计为6 bit,再在FPGA内部将接收到的数据串并转换为18 bit数据输出至液晶显示模块。因此在FPGA与单片机接口处,每个时钟FPGA仅接收R、G、B三组颜色数据中的一组D[5:0],经过FPGA的片内RAM缓存满480个D[5:0]以后再一次存储到一行DDR SDRAM中,同时给出存储单元的地址和各种控制信号。

硬件接口上,由于DDR SDRAM是高速器件,主要考虑与FPGA之间的互连。在布局布线时要求各数据线DQ和数据采样线DQS严格等长,以及采用FPGA对DDR SDRAM的专用接口。

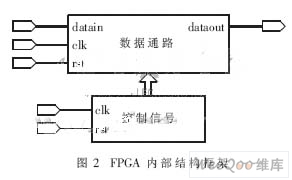

2 FPGA内部模块设计

高实时性是系统设计的基本要求。为统筹兼顾重要性各不相同的任务,一般采用时序和电路结构优化[6],以及各模块并行处理[7]实现。

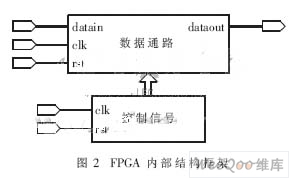

本系统中,3个主要器件都需要FPGA控制,且控制信号较多,数据通路设计又需考虑到3个时钟域的互相转换和相互通信,较为复杂。设计采用了自顶向下的模块化设计思路[8],将数据通路和数据控制通路分离,如图2。单独设计控制信号模块,并输入数据通路模块以控制和处理数据,使输出的数据达到设计要求。

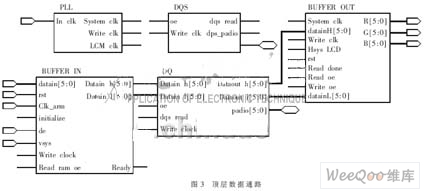

2.1 数据通路设计

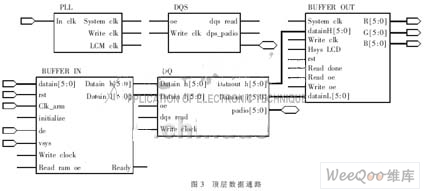

数据通路由如图3所示的模块构成。图中未标注的控制信号接口与控制信号模块相连。

PLL(Phase Lock Loop):锁相环是FPGA内部底层资源,此处将输入的50 MHz的时钟通过倍频、移相等得到系统所需的System clk(100 MHz,相位偏移0°)、Write clk(100 MHz,相位偏移-90°)和LCM clk(33 MHz,相位偏移0°)。

DQS:DQS信号控制模块,控制与DDR SDRAM的DQS引脚相连的DQS引脚,双向接口在使能信号oe的控制下产生或接收DQS信号,并将接收到的DQS信号移相90°以后作为FPGA内部对DQ数据组的采样信号。

BUFFER IN:输入缓存模块,在外部时钟和外部控制信号的作用下接收数据并缓存到片内RAM,每满480个数据发出一次Ready信号,表示缓存中已存满可占用一行DDR SDRAM存储单元的数据。

DQ:DQ数据控制模块,控制与DDR SDRAM的DQ引脚组相连的DQ引脚组,双向接口,在使能信号oe的控制下输出或接收DQ组数据。输出数据时使用Write clock,输入数据时使用DQS模块产生的dqs read信号对输入数据采样,并将结果输出到下级模块。

BUFFER OUT:输出缓存模块,缓存来自DDR SDRAM的数据,并在控制信号的控制下按LCM时序输出彩色图像数据。

2.2 控制模块设计

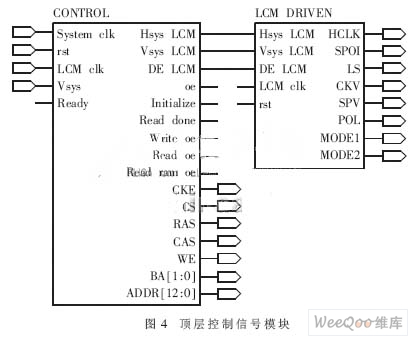

顶层控制信号模块由CONTROL模块和LCM DRIVEN模块两部分构成,如图4所示。主要负责各模块之间的通信,产生控制信号控制数据的流向,向各器件输出控制信号等。

CONTROL:控制模块,为DDR SDRAM分配读、写时间:以200 MHz的数据率在读时间段读出5行DDR SDRAM中的数据,缓存到BUFFER OUT,再以33 MHz的速度读出并输出到LCM;在写时间段探测数据通路中的BUFFER IN中的数据是否缓存完成,若完成则产生信号开始对DDR SDRAM写入数据。在DDR SDRAM的读写过程中根据需要产生DDR SDRAM控制信号、读写行列地址信号,为驱动LCM产生控制信号:行、场同步信号(Hsys LCM、Vsys LCM),数据有效信号(DE LCM)。

LCM DRIVEN:LCM驱动模块,输入LCM的控制信号,产生LCM驱动所需的各种控制信号,并输出到FPGA的I/O,结合外围电路,驱动LCD。

3 实现结果

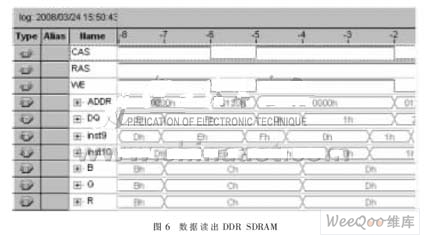

数据接口利用Altera公司专用SignalTapⅡ逻辑分析仪验证。图5、图6是用逻辑分析仪截取的芯片运行时在各引脚或逻辑单元处的实时波形图。图5表示数据输入FPGA直到进入DDR SDRAM的数据通路部分。数据输入经缓冲模块后按照进入FPGA的顺序,分奇偶两路(Qj、Qo)进入DQ接口模块,并合并成一路双倍速经DQ端口输出FPGA。该过程同时输出CAS、RAS、WE等命令信号和地址信号(ADDR)。由于设定了逻辑分析仪以系统时钟100 MHz速率采样各信号,因此对于数据率是200 MHz的DQ双向口,该采样信号只能间隔一个数据采样一次,而不能完全反映出DQ输出口的数据率。

图6表示数据读出DDR SDRAM进入FPGA经缓冲输出FPGA的数据通路部分。DDR SDRAM在CAS、RAS、WE等命令信号和地址信号(ADDR)控制下,将对应地址存储单元的数据以200 MHz的双倍数据率经DQ双向I/O口输入FPGA,并经DQ接口模块转换为100 MHz的单倍数据率,分两路输出(inst9、inst10)。经输出缓冲模块缓存后,再转换为LCM模块所需的时钟频率33.33 MHz,并行输出FPGA。类似的,由于逻辑分析仪以系统时钟100 MHz速率采样,DQ输入口的数据率在图中不能完全反映出来。

至此,数据经过了设计中所有为其设置的模块和接口,包括输入接口、输入缓冲模块、DQ/DQS接口、输出缓冲模块和输出接口。

设计ARM输出数据时钟是0.3 MHz,随着数据逐渐经片内输入缓存输入DDR SDRAM替换掉原有数据,对应在屏上的图像也逐渐被替换,该验证过程说明DDR SDRAM在过程中起到了帧存储器的作用,设计的系统与预期要求相符。

该显卡系统以单片DDR SDRAM为显示存储器存储图像数据,以FPGA为控制中心,嵌入式系统仅需通过I/O口在需改变图像时输出一帧数据至显卡,不需实时提供数据流和各种显示器控制信号,从而使嵌入式微处理器有足够的时间控制其所在的自动化系统。

设计采用800×480分辨率液晶显示器为图像输出设备,具有面向微处理器的通用接口,可匹配数据输出时钟频率50 MHz以下的微处理器。由于系统图像数据来自单片机,因此分立的系统没有数据来源,为了验证设计的正确性,验证步骤里采用了周立功单片机有限公司的EasyARM2131开发板验证设计结果。验证结果表明,设计达到了预期要求。

1 资源有限性法则 嵌入式计算不仅需要网络快速、一致的计算,而 且也要求系统能够井然有序地将其执行代码和数 据,存储在一个“ 共同” 的“ 狭小” 的空间内。

2 鲁棒性法则 嵌入式计算不仅要求系统迅速而有效的计算,而且还要求在某些计算单元出现错误的时候,系统仍然能 够继续正常运行工作。

3 实时性法则嵌入式系统的计算结果,不仅依赖于系统的逻辑运算之正确性,而且也依赖于这个运算结果的计算时间。

4 冗余度法则 在嵌入式系统具有足够的冗余度之后,系统的“ 初始敏感性” 对于其“ 最终计算结果” 的影响就变得微乎其微了。

5 结构性法则 对于嵌入式系统而言,其结构复杂性的趋势表明: a 系统结构越简单越有效(The [已过滤]st is the best) ; b 系统结构越复杂越稳定(More complex is more stable) 。

6 简约性法则 当简约一个嵌入式系统时,系统剩下的功能之 间的互动关系就会变得越来越强; 当系统的功能被简约之后,外来的入侵者之成 功的概率就会变得越来越大。

7 保育性法则 如果在嵌入式系统中要想保留某个系统功能, 是将所有的其他功能都看成是 “ 神圣不可侵 犯的 ” ; 系统的功能被移出(灭绝)或者生成(入 侵),一定会造成整体(群集)结构及其动态 性能上的重大转变。

8 组织性法则 嵌入式互联网(embedded Internet) 最重要的往往不是网络中个体设备的特质,而是存在于网络中的整体秩序,即 网络秩序 。 在一个高冗余度网络中,设备的单一作用已经不再能够构成影响到系统整体性能的主要因素 了,而起主要作用的是所有结点及其所构成的 连结 特征。

9 网络性法则 由一群设备相互作用的嵌入式Internet 结点所构成的网络,其整体所表现出的性质,往往与个别结点的 性质没有重大关系。

10 消息性法则 保证查寻消息:它具有严格的时间敏感或者基本常态 系统*作要求,这类消息要求一个来自系统的时间保 证。即一旦由这类消息引起的活动或者任务被执行,那么在确定的时间间隔内,它们的时间限定性必将被 系统所保证。 效果消息:它具有典型的软时间限定性,即其时 间限定是由活动或者任务本身的时间序列所规定,无 需系统保证就能满足其时间限定性的要求。

11 免疫性法则 嵌入式互联网(embedded Internet) 的免疫系统应当是一个仿生命体机 制,免疫功能是一个“前馈”系统,所以要求系统应具有预见能力,从而可以“以(小)毒攻(大)毒”。

12 融合性法则 嵌入式Internet 是一个复杂网络,将复杂网络结构用简单的“组成”来解析,让系统可以由孤立的“组成”来诠释“整体”,或者让系统可以由“结点”来表达“全局”。

13 性价比法则 如果系统A 是系统B 地嵌入式系统,即B(a) ,那么 系统A 的成本应不超过系统B 成本的10 %,而系统B(a) 的成本应大于系统A 和系统B 成本之和,系统B(a) 的性价比应提高30 %。

在嵌入式系统硬件设计中,串扰是硬件工程师必须面对的问题。特别是在高速数字电路中,由于信号沿时间短、布线密度大、信号完整性差,串扰的问题也就更为突出。设计者必须了解串扰产生的原理,并且在设计时应用恰当的方法,使串扰产生的负面影响降到最小。

1 串扰理论分析

串扰主要源自两个相邻导体之间所形成的互感与互容。在高速数字电路中,互感通常比互容的问题更严重。

1.1 互容

一个电路产生电场,该电场会影响第二个电路,这种相互影响的系数称为它们的互容。

式中,CM为互容,ΔV为驱动波形的阶跃幅度,TR是驱动波形的上升时间,RB是接收电路的接地阻抗。

由式1可知,互容串扰电压与CM、ΔV/TR 、成正比,因此,减小互容串扰电压的方法有:

① 减小CM。增大信号走线间距(因为互容与信号间距成反比,关键信号可采用3W原则)。

② 减小ΔV/TR。在确保信号时序的前提下,尽可能选择信号沿较缓的器件。

③ 减小RB。减小被干扰电路接地阻抗,对被干扰电路进行末端端接,为被干扰电路并接去耦电容。

1.2 互感

两个信号回路相互靠近时,一个信号回路的磁场变化将影响另一个信号回路,这种影响就是互感。互感的大小取决于信号回路的自感与两个信号回路耦合的程度。

式中,LM为互感,ΔV为驱动波形的阶跃幅度,TR是驱动波形的上升时间,RA是驱动电路的源端阻抗。

由式(2)可知,互感串扰电压与LM、ΔV/TR 成正比,与RA成反比。因此,减小互感串扰电压有如下方法。

(1) 减小LM

① 增大信号走线间距(因为LM随着间距平方的增加而下降,关键信号可采用3W原则)。

② 为信号提供完整的参考平面。在低速电路中,电流沿着电阻最小路径前进,而高速信号沿着电感最小路径前进。电感最小的返回路径就紧贴在一个信号导体下面,它使输出电流路径与返回电流路径之间的总回路面积最小,从而使输出电流路径与返回电流路径的干扰磁场相互抵消。

③ 减小信号到参考平面的距离,从而减小环路面积,达到减小LM的目的。

④ 尽可能地减小相邻信号间的平行长度。平行长度越短,则总的LM越小。

⑤ 无参考平面隔离的相邻信号层走线方向应该垂直,可减小磁场耦合程度。

⑥ 对串扰较敏感的信号线尽量布在内层,以减小磁场耦合程度。

(2) 减小ΔV/TR

在确保信号时序的前提下,尽可能选择信号沿较缓的器件。

(3) 增大RA

在干扰电路源端串接电阻,减小电流变化斜率,同时要兼顾与传输线阻抗匹配,避免信号反射。

1.3 近端串扰和远端串扰

图1 两条传输线的耦合

如图1所示,假设位于A点的驱动器是干扰源,而位于D点的接受器为被干扰对象,那么驱动器A所在的传输线被称为“干扰源网络”或“侵害网络(Agreessor)”,相应的接收器D所在的传输线网络被称为“静态网络”或“受害网络”。静态网络靠近干扰源一端的串扰称为“近端串扰”(也称后向串扰),而远离干扰源一端的串扰称为“远端串扰”(也称前向串扰)。根据产生的原因不同,可将串扰分为容性耦合串扰和感性耦合串扰两类。

受侵害线上近端和远端串扰噪声的波形可以通过图2得出。当一个数字脉冲上升沿进入传输线,它将不断地在受侵害线上感应出噪声,一部分串扰噪声将传向近端,另一部分将传向远端。远端串扰脉冲与侵害线上的信号经过时间TD(信号在传输线上的延迟时间)后同步到达终端。近端串扰脉冲将起始于侵害线上信号变化沿出现的时刻,而侵害信号到达终端前产生的一部分近端串扰信号将在t=2TD时刻才到达近端,这是因为这部分信号要经过整条传输线才能被传回近端。所以,近端串扰起始于t=0,并且持续2TD的时间。远端串扰起始于t=TD,持续时间为数字信号的上升或者下降时间。

图2 串扰噪声示意图

近端和远端传播的容性耦合电流都是正向的。具体的容性耦合如图3所示,图中的TP是干扰信号在传输线上的延迟时间,Tr是干扰信号的上升时间。

流向近端的感性耦合电流与近端容性耦合电流同向,流向远端的感性耦合电流与远端容性耦合电流反向。具体的感性耦合如图4所示。

图3 容性耦合的近端、远端串扰波形

图4感性耦合的近端、远端串扰波形

正常条件下,在一个完整平面上,感性和容性的串扰电压大小基本相等。远端的串扰分量(在D点的电压)相互抵消,近端的串扰分量(在C点的电压)相互增强。带状线电路具有很好的感性和容性耦合平衡性,因此其远端耦合系数极小;对于微带线路,与串扰相关的电场大部分穿过空气(而不是其他的绝缘材料),介电常数较小,因此容性串扰比感性串扰小,导致其远端串扰是一个小的负数。在开槽和其他不完整的参考平面上,感性耦合比容性耦合更大,使远端串扰变大。

1.4 串扰的反射

电压反射系数ρ的计算公式:

式中,RL是终端负载电阻,Z0是传输线特性阻抗。若RL =Z0,则ρ=0;若终端开路(RL=∞),则ρ=1;若终端短路(RL=0),则ρ=-1。在图1中,若近端阻抗与传输线特性阻抗不匹配,会使近端串扰在远端造成反射。为了消除近端串扰反射到远端,可以通过在近端接入正确的匹配电阻使ρ=0,消除反射。

2 串扰理论的应用实例

在工作实践中,笔者遇到了很多有关串扰的实际案例,通过运用上述分析的结论,均较好地得以解决。现将几个代表性问题的解决方法与大家分享。

2.1 增大信号走线间距

现象:Linux操作系统在加载过程中,出现偶然性意外错误而终止,系统提示访问了非法地址。

分析:操作系统从NAND Flash解压到SDRAM中并执行。SDRAM的CLK信号频率较高、沿斜率较大,本身就是一个干扰源。同时,由于CLK信号对于SDRAM时序控制的重要性,若受到周围信号的干扰,则可能影响SDRAM的正常读写。用示波器测试SDRAM的CLK信号,发现信号上偶尔会出现一些很小的干扰,但系统加载却正常了。经分析,这应与示波器探头自带的电容有关。尝试在CLK信号与地之间并接10 pF去耦电容,系统加载即正常。可见,CLK信号确实是受到了干扰,并接去耦电容正是将干扰滤除了一部分。

解决:由于SDRAM是高速器件,时序要求较高,CLK并接电容后,信号沿变缓,时序参数较为临界,通过增大信号走线间距的方法解决串扰问题更为合适。重新设计PCB时,将CLK与信号其他信号的中心距增大到3W(即3倍线宽),问题得以解决。

2.2 在信号源端串接电阻

现象:CPU通过总线外扩一个以太网芯片,但程序无法正常初始化该芯片,网络不通。

分析:用示波器测试“读”、“写”、“片选”、“数据”、“地址”等总线信号,发现这些信号上升、下降沿时间很短,信号过冲较严重,信号间距受空间所限无法增大,因此,总线信号间必然存在串扰问题。各总线信号既是干扰源,又是被干扰对象。在信号源端串接电阻有两个好处:作为干扰源,源端阻抗变大,电流变化率降低,与其他信号的互感耦合减小;作为被干扰对象,源端阻抗与传输线匹配,有利于吸收近端串扰,避免将近端串扰反射到远端。

解决:将总线信号源端串联电阻的阻值从10 Ω增大到50 Ω,重新运行程序,网卡芯片初始化正常,串扰问题解决。

2.3 为信号提供完整的参考平面

现象:CPU总线上增加点阵液晶设备,发现网口通信时网口1经常出现丢包现象,网口2甚至无*INK UP成功。

分析:系统主板为两层板,没有完整的信号参考平面,由于液晶连接线较长,使数据总线的长度增加,从而使串扰变得更加严重。网卡芯片与点阵液晶共用低8位数据总线与读、写控制信号,因此信号受到干扰、通信受到影响。

解决:重新设计PCB时,将2层板改为4层板,增加地层、电源层,为总线信号提供完整的参考平面,串扰减小。

2.4 减小被干扰电路接地阻抗

现象:SPI通信时,从SPI设备读回的数据不是期望的数据。

分析:用示波器测试SPI总线信号,发现CLK信号的上升沿、下降沿产生高频振荡,并两次跨过高、低门限电平。这将引起SPI数据的误触发,使CPU得到不正确的数据,因此需要滤除该高频干扰信号。

解决:在CLK信号与地之间并接1000 pF去耦电容,为高频干扰信号提供对地的低阻抗通道,干扰问题解决。

结语

串扰在高速电路设计中是一个不可忽视的问题,会影响系统的时序、降低噪声容限,导致系统无法正常工作。本文介绍了串扰产生的原理,通过对串扰电压的计算推导得到影响串扰的关键因素,根据这些因素提出一系列解决串扰问题的方法,并在实例中进行验证应用,对于解决串扰问题有一定的借鉴、指导意义。

维库电子通,电子知识,一查百通!

已收录词条937245个