UART即为Universal Asynchronous Receiver/Transmitter,译为通用异步收发器。UART是设备间进行异步通信的关键模块,用于控制计算机与串行设备的芯片。它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

计算机与外部设备的连接,基本上使用了两类接口:串行接口与并行接口。并行接口是指数据的各个位同时进行传送,其特点是传输速度块,但当传输距离远、位数又多时,通信线路变复杂且成本提高。串行通信是指数据一位位地顺序传送,其特点是适合于远距离通信,通信线路简单,只要一对传输线就可以实现双向通信,从而大大降低了成本。

串行通信又分为异步与同步两类。UART(Universal Asynchronous Receiver/Transmitter,通用异步收发器)正是设备间进行异步通信的关键模块。它的重要作用如下所示:

处理数据总路线和串行口之间的串/并、并/串转换;

通信双方只要采用相同的帧格式和波特率,就能在未共享时钟信号的情况下,仅用两根信号线(Rx 和Tx)就可以完成通信过程;

采用异步方式,数据收发完毕后,可通过中断或置位标志位的方式通知微控制器进行处理,大大提高微控制器的工作效率。

若加入一个合适的电平转换器,如SP3232E、SP3485,UART 还能用于RS-232、RS-485 通信,或与计算机的端口连接。UART 应用非常广泛,手机、工业控制、PC 等应用中都要用到UART。

1. 发送/接收逻辑

发送逻辑对从发送FIFO 读取的数据执行“并→串”转换。控制逻辑输出起始位在先的串行位流,并且根据控制寄存器中已编程的配置,会面紧跟着数据位(注意:位 LSB 先输出)、奇偶校验位和停止位。

在检测到一个有效的起始脉冲后,接收逻辑对接收到的位流执行“串→并”转换。此外还会对溢出错误、奇偶校验错误、帧错误和线中止(line-break)错误进行检测,并将检测到的状态附加到被写入接收FIFO 的数据中。

2. 波特率的产生

波特率除数(baud-rate divisor)是一个22 位数,它由16 位整数和6 位小数组成。波特率发生器使用这两个值组成的数字来决定位周期。通过带有小数波特率的除法器,在足够高的系统时钟速率下,UART 可以产生所有标准的波特率,而误差很小。

3. 数据收发

发送时,数据被写入发送FIFO。如果UART 被使能,则会按照预先设置好的参数(波特率、数据位、停止位、校验位等)开始发送数据,一直到发送FIFO 中没有数据。一旦向发送FIFO 写数据(如果FIFO 未空),UART 的忙标志位BUSY 就有效,并且在发送数据期间一直保持有效。BUSY 位仅在发送FIFO 为空,且已从移位寄存器发送一个字符,包括停止位时才变无效。即 UART 不再使能,它也可以指示忙状态。BUSY 位的相关库函数是UARTBusy( )

在UART 接收器空闲时,如果数据输入变成“低电平”,即接收到了起始位,则接收计数器开始运行,并且数据在Baud16 的第8 个周期被采样。如果Rx 在Baud16 的第8 周期仍然为低电平,则起始位有效,否则会被认为是错误的起始位并将其忽略。

如果起始位有效,则根据数据字符被编程的长度,在 Baud16 的每第 16 个周期对连续的数据位(即一个位周期之后)进行采样。如果奇偶校验模式使能,则还会检测奇偶校验位。

,如果Rx 为高电平,则有效的停止位被确认,否则发生帧错误。当接收到一个完整的字符时,将数据存放在接收FIFO 中。

4. 中断控制

出现以下情况时,可使UART 产生中断:

FIFO 溢出错误

线中止错误(line-break,即Rx 信号一直为0 的状态,包括校验位和停止位在内)

奇偶校验错误

帧错误(停止位不为1)

接收超时(接收FIFO 已有数据但未满,而后续数据长时间不来)

发送

接收

由于所有中断事件在发送到中断控制器之前会一起进行“或运算”操作,所以任意时刻 UART 只能向中断产生一个中断请求。通过查询中断状态函数UARTIntStatus( ),软件可以在同一个中断服务函数里处理多个中断事件(多个并列的if 语句)。

5. FIFO 操作 FIFO 是“First-In First-Out”的缩写,意为“先进先出”,是一种常见的队列操作。 Stellaris 系列ARM 的UART 模块包含有2 个16 字节的FIFO:一个用于发送,另一个用于接收。可以将两个FIFO 分别配置为以不同深度触发中断。可供选择的配置包括:1/8、 1/4、1/2、3/4 和7/8 深度。例如,如果接收FIFO 选择1/4,则在UART 接收到4 个数据时产生接收中断。

发送FIFO的基本工作过程: 只要有数据填充到发送FIFO 里,就会立即启动发送过程。由于发送本身是个相对缓慢的过程,因此在发送的同时其它需要发送的数据还可以继续填充到发送 FIFO 里。当发送 FIFO 被填满时就不能再继续填充了,否则会造成数据丢失,此时只能等待。这个等待并不会很久,以9600 的波特率为例,等待出现一个空位的时间在1ms 上下。发送 FIFO 会按照填入数据的先后顺序把数据一个个发送出去,直到发送 FIFO 全空时为止。已发送完毕的数据会被自动清除,在发送FIFO 里同时会多出一个空位。

接收FIFO的基本工作过程: 当硬件逻辑接收到数据时,就会往接收FIFO 里填充接收到的数据。程序应当及时取走这些数据,数据被取走也是在接收FIFO 里被自动删除的过程,因此在接收 FIFO 里同时会多出一个空位。如果在接收 FIFO 里的数据未被及时取走而造成接收FIFO 已满,则以后再接收到数据时因无空位可以填充而造成数据丢失。

收发FIFO 主要是为了解决UART 收发中断过于频繁而导致CPU 效率不高的问题而引入的。在进行 UART 通信时,中断方式比轮询方式要简便且效率高。但是,如果没有收发 FIFO,则每收发一个数据都要中断处理一次,效率仍然不够高。如果有了收发FIFO,则可以在连续收发若干个数据(可多至14 个)后才产生一次中断然后一并处理,这就大大提高了收发效率。

完全不必要担心FIFO 机制可能带来的数据丢失或得不到及时处理的问题,因为它已经帮你想到了收发过程中存在的任何问题,只要在初始化配置UART 后,就可以放心收发了, FIFO 和中断例程会自动搞定一切。

6. 回环操作

UART 可以进入一个内部回环(Loopback)模式,用于诊断或调试。在回环模式下,从Tx 上发送的数据将被Rx 输入端接收。

7. 串行红外协议

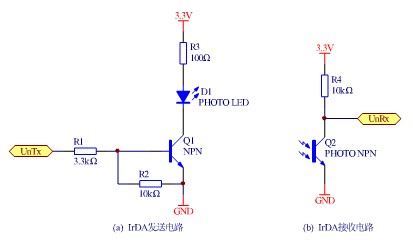

在某些 Stellaris 系列 ARM 芯片里,UART 还包含一个 IrDA 串行红外(SIR)编码器/ 解码器模块。IrDA SIR 模块的功能是在异步UART 数据流和半双工串行SIR 接口之间进行转换。片上不会执行任何模拟处理操作。SIR 模块的任务就是要给UART 提供一个数字编码输出和一个解码输入。UART 信号管脚可以与一个红外收发器连接以实现IrDA SIR 物理层连接。

如图所示,为UART 的IrDA SIR 模块基本应用电路。D1 为红外发射管,Q2 为红外接收管。

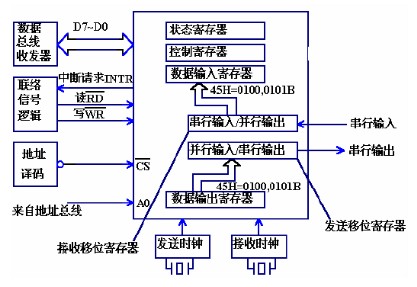

⑴输出缓冲寄存器,它接收CPU从数据总线上送来的并行数据,并加以保存。

⑵ 输出移位寄存器,它接收从输出缓冲器送来的并行数据,以发送时钟的速率把数据逐位移出,即将并行数据转换为串行数据输出。

⑶ 输入移位寄存器,它以接收时钟的速率把出现在串行数据输入线上的数据逐位移入,当数据装满后,并行送往输入缓冲寄存器,即将串行数据转换成并行数据。

⑷ 输入缓冲寄存器,它从输入移位寄存器中接收并行数据,然后由CPU取走。

⑸ 控制寄存器,它接收CPU送来的控制字,由控制字的内容,决定通信时的传输方式以及数据格式等。例如采用异步方式还是同步方式,数据字符的位数,有无奇偶校验,是奇校验还是偶校验,停止位的位数等参数。

⑹状态寄存器。状态寄存器中存放着接口的各种状态信息,例如输出缓冲区是否空,输入字符是否准备好等。在通信过程中,当符合某种状态时,接口中的状态检测逻辑将状态寄存器的相应位置“1”,以便让CPU查询。

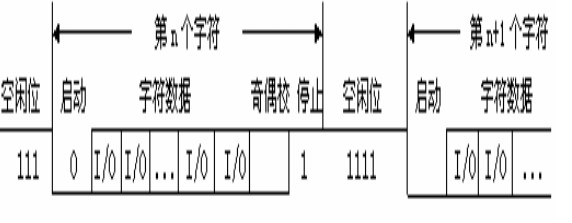

① 起始位:先发出一个逻辑”0”信号,表示传输字符的开始。

② 数据位:紧接着起始位之后。数据位的个数可以是4、5、6、7、8等,构成一个字符。通常采用ASCII码。从位开始传送,靠时钟定位。

③ 奇偶校验位:数据位加上这一位后,使得“1” 的位数应为偶数(偶校验)或奇数(奇校验),以此来校验数据传送的正确性。

④ 停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。

⑤空闲位:处于逻辑“1”状态,表示当前线路上没有数据传送。

维库电子通,电子知识,一查百通!

已收录词条308935个