通用可编程器件(Generic Array Logic,GAL)是Lattice公司于1985年首先推出的新型可编程逻辑器件。在工艺上,通用可编程器件采用了EEPROM的浮栅技术,具有可擦除、可重新编程和可长期保存数据等优点。在结构上,GAL器件在输出端设置了可编程的输出逻辑宏单元(OLMC-Output Logic Macro Cell),通过编程可以将OLMC设置成不同的输出方式。不仅完全兼容PAL,而且比PAL功能更全面。同一型号的GAL器件可以实现PAL器件所有的各种输出电路工作模式,即取代了大部分PAL器件。

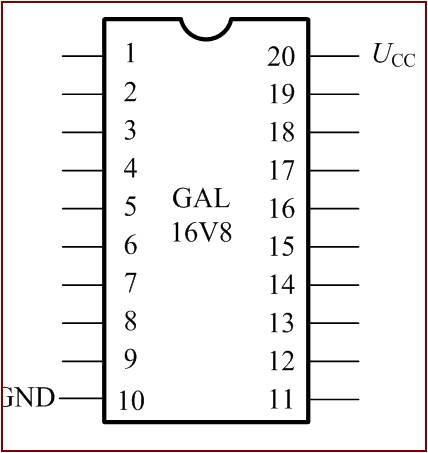

●8个输入缓冲器

●8个输出反馈/输入缓冲器

●8 个三态缓冲器

●8个输出逻辑宏单元OLMC,每个OLMC对应1个I/O引脚。

●由8×8个与门构成的与阵列,共形成64个乘积项,每个与门有 32 个输入项,由8个输入的原变量、反变量(16)和8 个反馈信号的原变量、反变量(16)组成,故可编程与阵列共有 32×8×8=2048 个可编程单元。

●系统时钟CK的输入缓冲器。

●三态输出选通信号OE的输入缓冲器

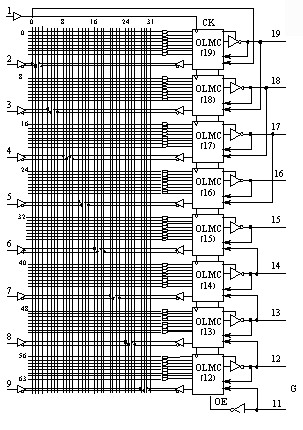

图为输出逻辑宏单元(OLMC)的内部结构,每个OLMC包含或门阵列中的一个或门。一个或门有 8 个输入端,和来自与阵列的 8 个乘积项(PT)相对应。其中 7 个直接相连,个乘积项(图中最上边的一项)经PTMUX相连或门输出为有关乘积项之和。 ●异或门的作用是选择输出信号的极性。当XOR(n)为1时, 异或门起反相器作用,否则起同相器作用。XOR(n)是控制字中的一位,n为引脚号。 ●D触发器(寄存器)对异或门的输出状态起记忆(存储)作用,使GAL适用于时序逻辑电路。 ●4个多路开关(MUX)在结构控制字段作用下设定输出逻辑宏单元的组态。 ●PTMUX是乘积项选择器,在AC1(n)·AC0控制下选择乘积项或地(0)送至或门输入端。 ●OMUX是输出类型选择器,在AC1(n)+AC0控制下选择组合型(异或门输出)或寄存型(经D触发器存储后输出)逻辑运算结果送到输出缓冲器。 ●TSMUX是三态缓冲器的使能信号选择器,在AC1(n)和AC1控制下从UCC、地、OE或乘积项中选择 1 个作为输出缓冲器的使能信号。 ●FMUX是反馈源选择器。在AC1(n)、AC0控制下选择D触发器的Q、本级OLMC输出、邻级OLMC的输出或地电平作为反馈源送回与阵列作为输入信号。

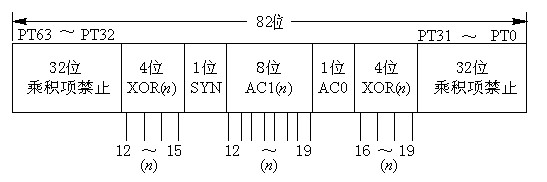

通用阵列逻辑的结构控制字共 82 位,每位取值为“1”或“0”,如图所示。图中XOR(n)和AC1(n)字段下的数字对应各个OLMC的引脚号。

SYN决定GAL器件是具有寄存器型(时序型)输出能力(SYN=0),还是纯粹组合型输出能力(SYN=1)。在OLMC(12)和OLMC(19)中,SYN还替代AC1(n),SYN替代AC0作为FMUX的选择输入,以维护与PAL器件的兼容性。

AC0、AC1(n)方式控制位。8个OLMC公用1位AC0。AC1(n)共 8 位,每个OLMC(n)有1位,n为引脚号(12~19)。 AC0, AC1(n)两者配合控制各MUX的工作。

XOR(n)极性控制位,共8位,每个OLMC(n)有1位,它通过异或门来控制输出极性。XOR(n)=0时,输出低有效;XOR(n)=1时,输出高有效。

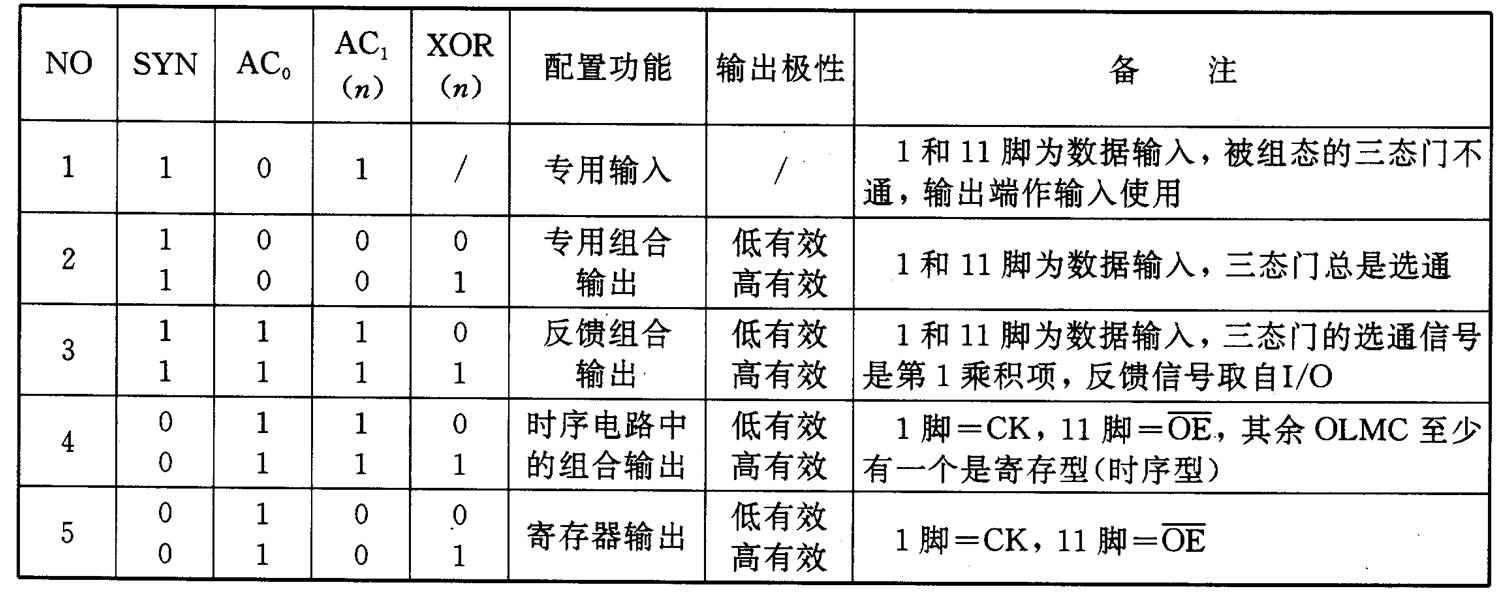

PT(n)积项禁止位,共64位,和与阵列中64个乘积项(PT0~PT63)相对应,用以禁止(屏蔽)某些不用的乘积项。在SYN、AC0、AC1(n)组合控制下,OLMC(n)可组态配置成5种工作模式。图中(a)~(e)分别表示不同配置模式下OLMC的等效电路。OLMC组态的实现,即结构控制字各控制位的设定都是由开发软件和硬件自动完成的。

从以上分析看出GAL器件由于采用了OLMC,所以使用更加灵活,只要写入不同的结构控制字,就可以得到不同类型的输出电路结构。这些电路结构完全可以取代PAL器件的各种输出电路结构。

①采用电擦除工艺和高速编程方法,编程方便、快速。整个芯片改写只需数秒钟,一片可改写 100 次以上。

②采用高性能的E2CMOS工艺,保证了GAL的高速度和低功耗。存取速度为 12~40 ns,功耗仅为双极性PAL器件的1/2 或 1/4,编程数据可保存 20 年以上。

③采用可编程的输出逻辑宏单元(OLMC),使得GAL器件对复杂逻辑门设计具有极大的灵活性。

④可预置和加电复位全部寄存器,具有 100%的功能可测试性。

⑤备有加密单元,可防止他人抄袭设计电路。

⑥备有电子标签(ES),方便了文档管理, 提高了生产效率

维库电子通,电子知识,一查百通!

已收录词条937245个