RAM即随机存取存储器,也称随机存储器或随机读/写存储器。RAM可以方便快速地直接从中任意存取出一个数据字或将数据字存入任一单元。这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。

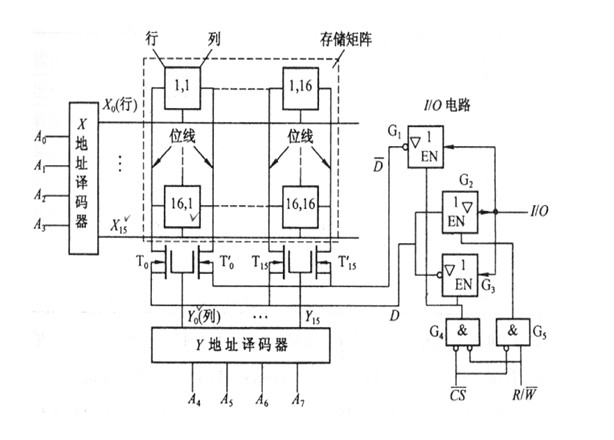

RAM主要有存储矩阵、地址译码器和读/写控制电路(I/O控制电路)三部分组成。

1.存储矩阵(数据线)

上图中点画线框内的美国小方块都代表一个存储单元,可以存储1位二值代码,存储单元可以是静态的(触发器),也可以是动态的(动态MOS存储单元)。这些存储单元一般都按阵列形式排列,形成存储矩阵,其目的是使地址译码更简单。

2.地址译码器(地址线)

分行地址译码器和列地址译码器两部分。

3.片选与I/O控制电路(控制线)

当一片RAM集成块不能满足存储容量的要求时,可以用若干片RAM连接成一个存储容量更大的满足要求的RAM,扩大存储容量的方法,通常有位扩展和字扩展两种。

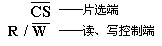

1.位扩展

存储器芯片的字长多数为1位、4位、8位等。当实际的存储系统的字长超过存储器芯片的字长时,需要进行位扩展。

位扩展方法:芯片的并联(地址线、控制线共用,数据线合并)

例如:下图为用两片8K×8位的芯片实现的8K×16位的存储器。

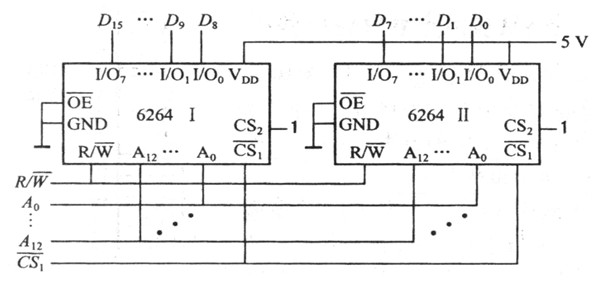

2.字扩展

方法:地址线、数据线和读写控制线连接在一起,而外加译码器控制各个芯片的片选端(/CS)。下图是四片8K×8 位RAMà32K×8 位。

图中,译码器的输入是高位地址A14、A13,译码器的输出连接各片RAM的片选信号。若A14A13=01,则RAM(2)片的/CS=0,其余各片RAM的/CS均为1,故选中第二片。读出的内容则由低位地址A12~A0决定。显然,四片RAM轮流工作,任何时候,只有一片RAM处于工作状态,整个系统字数扩大了四倍,而字长仍为八位。

1、随机存取

所谓“随机存取”,指的是当存储器中的消息被读取或写入时,所需要的时间与这段信息所在的位置无关。相对的,读取或写入顺序访问(Sequential Access)存储设备中的信息时,其所需要的时间与位置就会有关系(如磁带)。

2、易失性

当电源关闭时RAM不能保留数据。如果需要保存数据,就必须把它们写入一个长期的存储设备中(例如硬盘)。RAM和ROM相比,两者的区别是RAM在断电以后保存在上面的数据会自动消失,而ROM不会。

3、高访问速度

现代的随机存取存储器几乎是所有访问设备中写入和读取速度最快的,取存延迟也和其他涉及机械运作的存储设备相比,也显得微不足道。

4、需要刷新

现代的随机存取存储器依赖电容器存储数据。电容器充满电后代表1(二进制),未充电的代表0。由于电容器或多或少有漏电的情形,若不作特别处理,数据会渐渐随时间流失。刷新是指定期读取电容器的状态,然后按照原来的状态重新为电容器充电,弥补流失了的电荷。需要刷新正好解释了随机存取存储器的易失性。

5、对静电敏感

正如其他精细的集成电路,随机存取存储器对环境的静电荷非常敏感。静电会干扰存储器内电容器的电荷,引致数据流失,甚至烧坏电路。故此触碰随机存取存储器前,应先用手触摸金属接地。

1.静态存储单元(SRAM)

●存储原理:由触发器存储数据

●单元结构:六管NMOS或CMOS构成

●优点:速度快、使用简单、不需刷新、静态功耗极低;常用作Cache

●缺点:元件数多、集成度低、功耗大

●常用的SRAM集成芯片:6116(2K×8位),6264(8K×8位),62256(32K×8位),2114(1K×4位)

2.动态存储单元(DRAM)

●存贮原理:利用MOS管栅极电容可以存储电荷的原理,需刷新(早期:三管基本单元;现在:单管基本单元)

●刷新(再生):为及时补充漏掉的电荷以避免存储的信息丢失,必须定时给栅极电容补充电荷的操作

●刷新时间:定期进行刷新操作的时间。该时间必须小于栅极电容自然保持信息的时间(小于2ms)。

●优点: 集成度远高于SRAM、功耗低,价格也低

●缺点:因需刷新而使外围电路复杂;刷新也使存取速度较SRAM慢,所以在计算机中,DRAM常用于作主存储器。

尽管如此,由于DRAM存储单元的结构简单,所用元件少,集成度高,功耗低,所以目前已成为大容量RAM的主流产品。

维库电子通,电子知识,一查百通!

已收录词条937245个