对已完成的SRAM存储器主板进行操作。在MSDOS模式下启动,利用DEBUG指令,从D0000h开始试着进行数据的读/写操作。如果确认了主板能够正常运行,则为各份电源连接器(CN2)提供电源,去掉个人计算机的电源,损耗电流在40μA左右。重新启动MS-DOS模式,读取刚才写人的地址,因为能够读出所写人的数据,因而可知各份电源是起到了相应的作用的。

由于从D0000h开始的领域为PC/AT的扩展BIOS领域,所以,如果SRAM上事先写入了附加头信息等的数据,则在操作系统启动前将被调用。在SRAM上安装各种经过仔细研究的程序进行试验,你就会有非常有趣的发现。

SRAM与闪速存储器等不同,它的替换操作是非常简单的,可以以1字节为单位进行替换,并且不需要替换时间。一旦拔掉电池数据将丢失,因而在实施ROM化之前的阶段,可以进行各种各样的实验,这是其方便之处。

1. 地址缓冲器

在提供给存储器的SA0~SA15地址中加人缓冲器。缓冲器利用74LS244也可以,但因为741LS245布线简单,所以通过74LS245可单向使用。

2. 数据缓冲器

因为数据需要双向进行,所以要利用74LS245进行接收。将栅极一直打开,通过对存储器的读信号来进行方向控制。本次我们采用将PLD上存储器的读信号设置为只在CS1有效时才输出的方法。

3. PLD(MEMDEC)

LD应用于生成对存储器的片选、DE以及WE信号中。片选信号是在刷新周期以外、当地址高位(SA16~SA19)为Dh(将D0000h~DFFFFh设置在SRAM主板空间)、且BALE为低电平时被选择的。

将存储器的读/写信号设置为当片选和SMEMR/SMEMW有效时输出。

4. 各份电源的切换

电池各份的重点在于电源切换和片选信号的控制。本次为了简单起见,只单纯获取Vcc和电池(为CN2提供3.6V的电池)的二极管OR,但需要注意二极管正向电压降。如果电源电压比所提供的电压低很多,则可能发生超出操作电压或者输入引脚的电压高于电源电压的情况。

5. 片选控制

为了电池备份,必须使存储器的片选信号无效。本次我们虽然只利用CE1进行控制,但为了保持较低的损耗电流,必须使CE1可保持与电源电压相近的值(CY62l28为VCC-0.2V以上)。为了进行片选控制,将利用作为电源监视IC的ADM708(模拟器件)和74HC系列的CMOS门组成电路。

ADM708本来是CPU用于生成复位信号的器件,这种用于电源监视的IC具有几个种类,还包括用于SRAM的电池各份的电源切换电路及内置片选控制功能的IC。利用这种IC的电路虽然非常简单,但器件的价格有些高,这是其缺点所在。

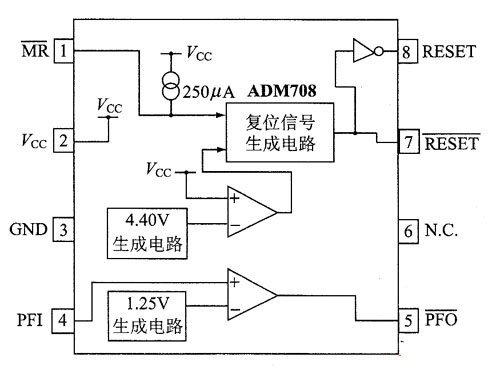

我们本次利用的ADM708引脚配置以及内部框图如图1所示。电源的切换关键在于电源电压下降到何种程度才能使之成为忽略主机信号的各份状态,由个别零部件进行这样的控制是相当麻烦的。

图1 ADM708的引脚配置与框图

从框图上可以明白,ADM708内部具各4.40V和1.25V的生成电路,4.40V的生成电路与Vcc相比较,增加了一个复位生成电路。当电源电压低于4.40V时,RESET/RESET信号有效(RESET为高电平,RESET为低电平)。

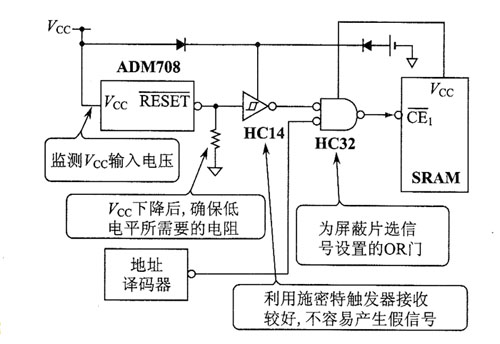

电路的操作如图2所示。因为Vcc自身将逐渐降低,而RESET方面的输出电压也将随之一块降低,为此我们这次将利用RESET的输出。当电源电压超出ADM708的操作范围时,为了确保低电平而增加下拉电阻,由74HC14的施密特触发器的栅极接受。74HC14以及下一阶段的74HC32的电源引脚与SRAM的电源引脚公用。

图2 备份电路的操作

因此,如果ADM708的RESET为低电平,则74HC32的输出引脚被强制为高电平,又因为SRAM的CE1无效,因而变为待机状态。

SRAM(静态随机存取存储器)是一种只要在供电条件下便能够存储数据的存储器件,而且是大多数高性能系统的一个关键部分。SRAM具有众多的架构,各针对一种特定的应用。本文旨在对目前市面上现有的SRAM做全面评述,并简要说明就某些特定用途而言,哪类SRAM是其选择。 SRAM从高层次上可以划分为两个大类:即同步型和异步型。同步型SRAM采用一个输入时钟来启动至存储器的所有事务处理(读、写、取消选定等)。而异步型SRAM则并不具备时钟输入,且必须监视输入以获取来自控制器的命令。一旦识别出某条命令,这些器件将立即加以执行。

同步SRAM家族分类

与某一特定应用相适应的SRAM的选择取决于多个因素,其中包括功率限制、带宽要求、密度以及读/写操作模式等。可满足不同系统要求的同步型和异步型SRAM多种多样,本文将逐一加以说明。

各种同步型SRAM比较

同步型SRAM于上个世纪80年代后期首度面市,最初是面向具有极高性能的工作站和服务器中的第二级(L2)高速缓冲存储器应用。进入上个世纪90年代中期之后,它又在较为主流的应用(包括个人电脑中的第二级高速缓冲存储器)中寻觅到了自己的用武之地。自那以后,在包括高性能网络在内的众多应用的设计中,同步型SRAM大行其道(在这些应用中,它们通常被用于数据缓冲器、高速暂存器、队列管理功能和统计缓冲器)。

同步型SRAM又可以采用多种不同的架构。下文将对某些“主流”的器件做简要说明。

1:标准同步型SRAM

标准同步型SRAM是被“主流应用”所接纳的种同步型SRAM。这些器件虽然主要面向PC L2高速缓冲存储器应用,但也渗透到了非PC应用领域中,比如网络、电信、数字信号处理(DSP)以及医疗和测试设备。其中,标准同步型SRAM具有两种基本格式:流水线型和直通型。两者之间的差异是:直通型SRAM仅在输入端上具有寄存器,当地址和控制输入被捕获且一个读存取操作被启动时,数据将被允许 “直接流”至输出端。当用户对初始延迟的重要性考虑超过对持续带宽的考究时,人们往往优先采用直通型架构。“流水线型”同步SRAM同时拥有一个输入寄存器和一个输出寄存器。流水线型SRAM所提供的工作频率和带宽通常高于直通型SRAM。因此,在需求较高宽带,而对初始延迟不是很敏感时,人们常常优先采用流水线型SRAM。

2:NoBLTM(无总线延迟)型SRAM

有些应用不允许“等待状态”。比如网络应用中“等待状态”有可能对性能产生严重的影响。为解决该问题,赛普拉斯公司推出了无总线延迟(NoBL)型SRAM。NoBL型SRAM与标准同步型SRAM很相似,但是拥有附加的片上逻辑电路,旨在完全消除标准同步型SRAM系列所需的“等待状态”。通过消除这些“等待状态”,此类SRAM能够实现100[%]的总线利用率(丝毫不受读/写模式的影响)。该功能极大地改善了存储器性能,尤其是当存在频繁的读/写操作变换时。

NoBL型SRAM也存在两种版本:直通型和流水线型。直通型NoBL SRAM始终具有一个单周期偏移,而NoBL流水线型SRAM则保持了一个双周期偏移。

3:四倍数据速率(QDRTM)型SRAM

尽管推出了NoBL型架构并使性能较之标准同步型SRAM有所改善,但某些系统对性能有着更高的要求。于是,赛普拉斯、Renesas、IDT、NEC和三星等几家公司联合开发出了QDR型SRAM。QDR架构旨在满足那些要求低延迟且所需带宽明显高于NoBL型架构提供能力的“高带宽需求型”系统的需要。 QDR型SRAM与NoBL型SRAM最为显着的差异之一是前者的读端口和写端口是分开的。这些端口可独立工作,并支持并行的读和写事务处理。QDR型 SRAM能够以DDR传输速率(2倍)来支持两项同时出现的事务处理,四倍数据速率(QDR)的名称便是由此得来的。

QDR型SRAM具有两种基本类型:即2字脉冲串和4字脉冲串。这两种类型之间的差异在于每项事务处理过程中所支持的脉冲串长度。

4:QDR-II型SRAM

QDR- II型SRAM与QDR型SRAM相似,但在性能方面进一步提升。与相同频率的QDR型器件相比,QDR-II型SRAM所产生的总数据有效窗口面积大了 35[%]左右。另外,QDR-II型SRAM产品还比QDR型器件多了一个半延迟周期。这增加的半个时钟周期可在对初始延迟影响极小的情况下提供高得多的频率和带宽。

5:DDR型SRAM

如果QDR型SRAM面向的是具有平衡读/写模式的应用,DDR型SRAM架构则主要针对那些需要进行数据流式传输(例如,后随多项写操作的多项读操作)、且所需带宽远远高于标准同步型器件或NoBL型器件的应用。DDR型SRAM具有出众的整体总线利用率以及高得多的总带宽,性能也因此得到了限度的提升。

和QDR型SRAM一样,DDR型SRAM也有两种格式:即2字脉冲串和4字脉冲串。究竟选择哪一种取决于所需的数据颗粒度以及存储器的数据总线宽度。

各种异步型SRAM比较

第二大类SRAM为异步型SRAM。那些不具备时钟输入的SRAM便是异步型的。在这些器件中,读操作和写操作将在器件接收到指令之后立即被启动。

采用异步型SRAM的优点之一是它们拥有长达几十年的使用历史并已为人们所充分了解。由于异步型SRAM已经面市很久了,因此许多标准处理器都包含了业已配备异步型SRAM接口的存储控制器,从而限度地减少了所需的设计工作量。异步型SRAM的典型存取时间为8ns(或更长)。因此,它们一般应用于时钟频率为100MHz(或更低)的系统中。异步型SRAM可被进一步划分为两种主要类别:即快速异步型SRAM和低功耗异步型 SRAM(MoBLTM)。

1:快速异步型SRAM

存取时间为35ns(或更短)的异步型SRAM可被归类为“快速”异步型SRAM。这些存储器通常应用于老式系统中,且功耗较高(1/2W或更高是司空见惯的)。其典型应用包括老式PC L2高速缓冲存储器、高速暂存器以及工业应用中的缓冲存储器。

2:MoBLTM低功耗异步型SRAM

有些应用(例如移动电话)对功耗的关注程度要超过对性能的关注程度。因此,制造商(比如赛普拉斯公司)推出了功耗极低的SRAM系列。赛普拉斯的 MoBL(意指“更长的电池使用寿命”)低功耗异步型SRAM产品库汇集了多款典型存取时间约为40ns(或更长)并专为实现低功耗而优化的器件。典型待机功耗可低至10μW(或更低),而运行功耗则可低至30mW(或更低)。这些器件的存储密度各异,从64Kb到16Mb一应俱全。

伪SRAM(亦即PSRAM)

如果需要16Mb以上的存储密度,则PSRAM(或称伪PSRAM)是一种可行的解决方案。所谓伪SRAM是指一种具有一个DRAM存储器内核和一个 “SRAM型”接口的存储器件。由于PSRAM使用了一个DRAM内核,因而也需要进行周期性的刷新,以便保存数据。但不同的是,标准DRAM的刷新控制是在器件外部进行的,而PSRAM则具有一个“隐式”刷新电路,这使得它们能够被容易地用作其他异步型SRAM的存储密度升级型器件。

结论

在选择SRAM时,您会面对众多的选择方案。在某些场合,选择是有限的。许多已经确立了自己稳固地位的处理器都包含了支持特殊SRAM架构的存储控制器。新型处理器的设计则更灵活。为了决定的可选方案,至关重要的是确定存储器子系统(即兆比特每秒、初始延迟、运行功耗、待机功耗、成本等等)的优先级以及系统的工作特性(读/写操作模式、工作频率等等)。

网络应用往往具有接近50/50的读/写模式,它适合于采用QDR系列的解决方案。其他应用(甚至是同一个系统内的功能电路)则往往具有不平衡的读/写模式,这就适合于采用公共I/O架构,包括标准同步型、NoBL型和DDR型。

另有一些系统要求可能的功耗,以便延长电池的使用寿命,可选用的方案分别为MoBL型SRAM和PSRAM。

静态随机存取存储器(SRAM)多年来被广泛应用于各种场合。凡是需要快速存取数据的应用,特别是在要求初始存取等待时间很短的情况下,都会考虑使用SRAM,这已经成为一个常识。历史上SRAM存储器市场曾经几度起伏,大多数时候,整个市场需求量会因为一个新的SRAM应用而暴涨。例如,1995年PC快速增长的时候,SRAM作为CPU的缓存,因而其需求量大幅增长。1999年网络市场,以及2003年手机市场的暴发,也使SRAM存储器市场出现了同样的情况。

然而,在过去的几年中,SRAM存储器市场由于种种原因急剧萎缩。市场调查数据显示,SRAM存储器市场容量已从2000年的60亿美元缩小到目前的十亿美元。市场容量的缩减也导致了供应商格局的变化,使得各厂商的SRAM部门收入增长潜力受到限制。这些厂商中很多是价值几十亿美元的公司,他们对市场容量更大的产品比较有兴趣。在过去的2、3年里,我们已经看到美光、摩托罗拉、IBM、东芝、三星、NEC、瑞萨全部或部分退出了SRAM存储器市场。

基于这种现状,人们不禁要问:SRAM会不会彻底死掉?我们相信,答案是否定的。从技术的角度来说,与竞争技术(例如SDRAM甚至RLDRAM)相比,SRAM仍然具有最短的初始存取等待时间。而其他产品的初始存取等待时间很难做到5个周期以内,而在SRAM的许多典型应用中,超过三个周期的等待就是不可接受的了,特别是网络和电信应用领域。另一方面,由于重新进行系统设计的高额成本,很多老的设计仍在使用SRAM并会继续使用相当长的一段时间。

过去几年中,SRAM供应商也针对不同应用需求开发了很多不同种类的SRAM。例如,高端网络设备需要很高速度的同步SRAM来为各类系统提供G级带宽。我们相信高速和超高速SRAM未来还将继续发展。这一驱动力源自于电信应用领域对更高频率的同步SRAM的持续需求。时钟速度已经从66Mhz提高到了300Mhz。为了向客户提供更多的带宽,同步SRAM产生了很多不同的架构,包括NoBL(无总线等待时间),QDR(四倍数据率),QDRII,以及现在的QDRII+。作为SRAM存储器市场的,赛普拉斯发起创立并从一开始起就是QDR联盟的成员。赛普拉斯还是个提供72M Sync/NoBL 和 QDR SRAM的供应商,这是世界上的SRAM。随着网络系统对带宽和速度的持续推动,SRAM已成为高端网络系统中重要的支持元件。

SRAM的另一分支是异步SRAM。这类SRAM不像同步SRAM那样依靠时钟输出数据,而是在某一特定时间内保证读写数/据。最老一代的SRAM是快速异步SRAM,速度一般在10ns~20ns。这些SRAM广泛应用于DSL、IP电话、BTS、VOIP、开关、医疗系统、打印/传真机、汽车导航系统等等。快速异步SRAM的供应商包括赛普拉斯、三星和瑞萨。然而,作为“长寿”策略的一部分,只有赛普拉斯保持了最丰富的产品线。赛普拉斯至今仍向客户供应4Kb SRAM,这一产品20年前就投产了。

异步SRAM的另一分支是低功耗SRAM。他们通常具有较低的访问速度,Taa在55ns或70ns。这类SRAM将功耗,特别是待机电流(Isb1, Isb2)降到了,以满足移动设备的要求。典型的Icc可以达到1mA且Isb1/Isb2降到1uA的水平。这类存储器在手机、消费电子、汽车、POS、打印机、医疗设备等领域有着广泛的应用。在各类低功耗SRAM存储器市场中,赛普拉斯的MoBLTM(更长电池寿命)SRAM鹤立鸡群,因其能在保持Isb2的同时达到45ns的Taa。

在的三个微功耗SRAM供应商中,三星最近退出了市场。瑞萨仍然保持着现有产品的供货,但是没有迹象表明他们会扩充其目前产品线。还在更新技术平台上开发新产品的供应商就是赛普拉斯,而且还保持着该领域最宽的产品线,这使得赛普拉斯成为这些细分市场中的一线供应商,并在过去的几个季度中引发了市场的重新洗牌。我们期待缺货和价格上涨能够为二线供应商带来利益,并催生异步SRAM存储器市场的新玩家。然而,对于二线和新供应商而言,这仍然是一场艰苦的攻坚战,因为存储器生意需要规模和长时间的学习经验。另一方面,随着赛普拉斯将90nm技术应用于微功耗SRAM,客户正在积极地向新的技术转移。对于新客户,这实际上是一个好机会,可以直接采用赛普拉斯的90nm技术并享受其容量和成本优势。

维库电子通,电子知识,一查百通!

已收录词条937245个