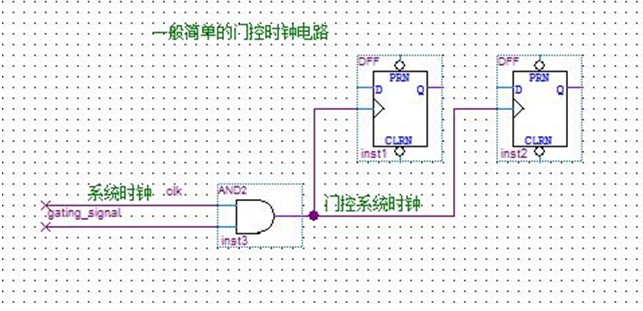

门控时钟,英文名gate clock。所谓“门控”是指一个时钟信号与另外一个非时钟信号作逻辑输出的时钟。比如,你用一个控制信号“与”一个CLK,以控制CLK的起作用时间。可以通过关闭芯片上暂时用不到的功能和它的时钟,从而实现节省电流消耗的目的。

在许多应用中,整个设计项目都采用外部的全局时钟是不可能或不实际的。PLD具有乘积项逻辑阵列时钟(即时钟是由逻辑产生的),允许任意函数单独地钟控各个触发器。然而,当你用阵列时钟时,应仔细地分析时钟函数,以避免毛刺。通常用阵列时钟构成门控时钟。门控时钟常常同微处理器接口有关,用地址线去控制写脉冲。然而,每当用组合函数钟控触发器时,通常都存在着门控时钟。如果符合下述条件,门控时钟可以象全局时钟一样可靠地工作:

1.驱动时钟的逻辑必须只包含一个“与”门或一个“或”门。如果采用任何附加逻在某些工作状态下,会出现竞争产生的毛刺。

2.逻辑门的一个输入作为实际的时钟,而该逻辑门的所有其它输入必须当成地址或控制线,它们遵守相对于时钟的建立和保持时间的约束。

所谓门控时钟就是指连接触发器时钟端来自于组合逻辑,凡是组合逻辑在布局布线之后肯定会产生毛刺,而如果采用这种有毛刺的信号来作为时钟使用的话将会出现功能上的错误。

组合逻辑中多用门控时钟,一般驱动门控时钟的逻辑都是只包含一个门,如果有其他的附加逻辑,就容易因竞争而产生不希望的毛刺。门控时钟通过一个时能信号控制时钟的开关。当系统不工作时可以关闭时钟,整个系统处于非激活状态,这样就能够在某种程度上降低系统功耗。然而,使用门控时钟并不符合同步设计的思想,它可能会影响设计的实现和验证。单纯从功能上看,使用使能时钟替代门控时钟是一个不错的选择;但是使能时钟在使能信号关闭时,时钟信号仍然在工作,它无法像门控时钟那样降低系统的功耗。

解决方案:

对于上升沿有效的系统时钟clk,他的下降沿先把门控时钟打一拍,然后再用这个使能信号和系统时钟clk相与后作为后续电路的门控时钟。

维库电子通,电子知识,一查百通!

已收录词条45650个