时间:2023/8/7 17:11:58

时间:2023/8/7 17:11:58

阅读:1198

阅读:1198

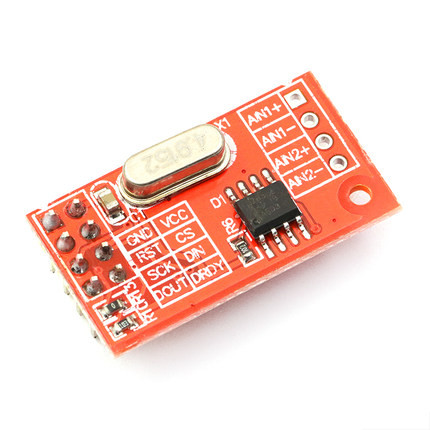

AD7705采用双列16脚封装。带信号调理、1mW功耗,是AD公司出品的适用于低频测量仪器的AD转换器。它能将从传感器接收到的很弱的输入信号直接转换成串行数字信号输出,而无需外部仪表放大器。采用Σ-Δ的ADC,实现16位无误码的良好性能,片内可编程放大器可设置输入信号增益。通过片内控制寄存器调整内部数字滤波器的关闭时间和更新速率,可设置数字滤波器的第一个凹口。在+3V电源和1MHz主时钟时, AD7705功耗仅是1mW。AD7705是基于微控制器(MCU)、数字信号处理器(DSP)系统的理想电路,能够进一步节省成本、缩小体积、减小系统的复杂性。应用于微处理器(MCU)、数字信号处理(DSP)系统,手持式仪器,分布式数据采集系统。

AD7705

产品型号 | AD7705 |

品牌商 | ADI |

工作电压 | 2.7 V至3.3 V或4.75 V至5.25 V |

功耗 | 最大1 mW(3 V) |

待机电流 | 最大8 μA |

封装类型 | 16引脚DIP、16引脚SOIC和TSSOP封装 |

两个全差分输入通道ADC

可编程增益前端

增益范围从1至128

三线串行接口

SPI?, QSPI?, MICROWIRE?, DSP兼容

SCLK上可接受施密特触发器输入

提供模拟输入缓冲

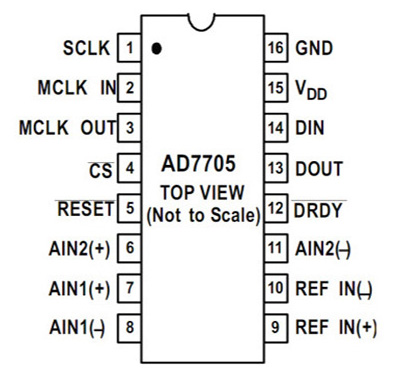

名称 | 功能 |

SCLK | 串行时钟,施密特逻辑输入。将一个外部的串行时钟加于这一输入端口,以访问AD7705/7706 的串行数据。和单片机传输数据时的控制时钟 |

MCLKIN | 为转换器提供主时钟信号。能以晶体/谐振器或外部时钟的形式提供。晶体/谐振器可以接在MCLKIN 和MCLKOUT 二引脚之间。此外,MCLKIN 也可用CMOS 兼容的时钟驱动, 而MCLKOUT 不连接。时钟频率的范围为500kHz~5MHz |

MCLKOUT | 当主时钟为晶体/谐振器时,晶体/谐振器被接在MCLKIN 和MCLKOUT 之间。如果在MCLKIN 引脚处接上一个外部时钟,MCLKOUT 将提供一个反相时钟信号。这个时钟可以用来为外部电路提供时钟源,且可以驱动一个CMOS 负载。如果用户不需要,MCLKOUT 可以通过时钟寄存器中的CLKDIS位关掉。这样,器件不会在MCLKOUT 脚上驱动电容负载而消耗不必要的功率 |

CS’ | 片选,低电平有效的逻辑输入,选择AD7705/7706。将该引脚接为低电平,AD7705/7706 能以三线接口模式运行(以SCLK、DIN 和DOUT 与器件接口)。在串行总线上带有多个器件的系统中,可由CS’对这些器件作出选择,或在与AD7705/7706 通信时,CS’可用作帧同步信号 |

RESET | 复位输入。低电平有效的输入,将器件的控制逻辑、接口逻辑、校准系数、数字滤波器和模拟调制器复位至上电状态 |

AIN2(+) | 差分模拟输入通道2的正输入端 |

AIN1(+) | 差分模拟输入通道1 的正输入端; |

REFIN(+) | 基准输入端,基准输入是差分的,并规定REFIN(+)必须大于REFIN(-)。REFIN(+)可以取VDD 和GND 之间的任何值 |

REFIN(-) | 基准输入端,REFIN(-)可以取VDD 和GND 之间的任何值,且满足REFIN(+)大于REFIN(-) |

DRDY’ | 逻辑输出。这个输出端上的逻辑低电平表示可从AD7705/7706 的数据寄存器获取新的输出字。完成对一个完全的输出字的读操作后,DRDY’引脚立即回到高电平。如果在两次输出更新之间,不发生数据读出,DRDY’将在下一次输出更新前500×tCLKIN 时间返回高电平。当DRDY’处于高电平时,不能进行读操作,以免数据寄存器中的数据正在被更新时进行读操作。当数据被更新后, |

DOUT | 串行数据输出端 |

DIN | 串行数据输入端 |

VDD | 电源电压,+3.3V |

GND | 内部电路的地电位基准点 |