直接数字频率合成是一种新的频率合成技术和信号产生的方法,具有超高速的频率转换时间、极高的频率分辨率分辨率和较低的相位噪声,在频率改变与调频时,DDS能够保持相位的连续,因此很容易实现频率、相位和幅度调制。此外,DDS技术大部分是基于数字电路技术的,具有可编程控制的突出优点。因此,这种信号产生技术得到了越来越广泛的应用,很多厂家已经生产出了DDS专用芯片,这种器件成为当今电子系统及设各中频率源的器件。

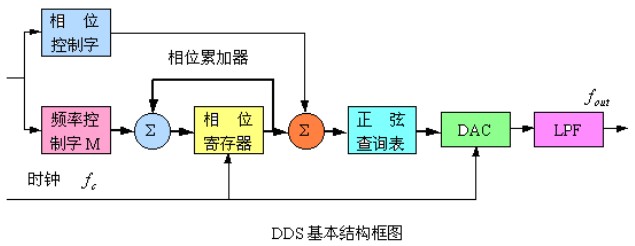

工作过程为:

1, 将存于数表中的数字波形,经数模转换器D/A,形成模拟量波形.

2, 两种方法可以改变输出信号的频率:

(1),改变查表寻址的时钟CLOCK的频率, 可以改变输出波形的频率.

(2), 改变寻址的步长来改变输出信号的频率.DDS即采用此法. 步长即为对数字波形查表的相位增量.由累加器对相位增量进行累加, 累加器的值作为查表地址.

3, D/A输出的阶梯形波形,经低通(带通)滤波,成为质量符合需要的模拟波形.

直接数字频率合成主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、低通平滑滤波器等构成。其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号用于DDS中各部件同步工作。DDS的实质是对相位进行可控等间隔的采样。

(1)输出频率相对带宽较宽 输出频率带宽为50%fs(理论值)。但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的 抑制,实际的输出频率带宽仍能达到40%fs。 (2)频率转换时间短 DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。事实上,在 DDS的频率控制字改变之后,需经过一个时钟周期之后按照新的相位增量累加,才能实现频率的转 换。因此,频率时间等于频率控制字的传输,也就是一个时钟周期的时间。时钟频率越高,转换时 间越短。DDS的频率转换时间可达纳秒数量级,比使用其它的频率合成方法都要短数个数量级。 (3)频率分辨率极高 若时钟fs的频率不变,DDS的频率分辨率就是则相位累加器的位数N决定。只要增加相位累加器的 位数N即可获得任意小的频率分辨率。目前,大多数DDS的分辨率在1Hz数量级,许多小于1mHz甚 至更小。 (4)相位变化连续 改变DDS输出频率,实际上改变的每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在 改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性。 (5)输出波形的灵活性 只要在DDS内部加上相应控制如调频控制FM、调相控制PM和调幅控制AM,即可以方便灵活地实 现调频、调相和调幅功能,产生FSK、PSK、ASK和MSK等信号。另外,只要在DDS的波形存储器 存放不同波形数据,就可以实现各种波形输出,如三角波、锯齿波和矩形波甚至是任意的波形。当 DDS的波形存储器分别存放正弦和余弦函数表时,既可得到正交的两路输出。 (6)其他优点 由于DDS中几乎所有部件都属于数字电路,易于集成,功耗低、 体积小、重量轻、可靠性高,且易于程控,使用相当灵活,因此性价 比极高。 DDS也有局限性,主要表现在: (1)输出频带范围有限 由于DDS内部DAC和波形存储器(ROM)的工作速度限 制,使得DDS输出的频有限。目前市场上采用CMOS、 TTL、ECL工艺制作的DDS工习片,工作频率一般在几十 MHz至400MHz左右。采用GaAs工艺的DDS芯片工作频 率可达2GHz左右。 (2)输出杂散大 由于DDS采用全数字结构,不可避免地引入了杂散。其来 源主要有三个:相位累加器相位舍位误差造成的杂散;幅 度量化误差(由存储器有限字长引起)造成的杂散和DAC 非理想特性造成的杂散。

1,采用高性能DDS单片电路的解决方案

2,采用分立IC电路系统实现,一般有CPU,RAM,ROM,D/A,CPLD,模拟滤波器等组成

3,CPLD,FPGA实现

维库电子通,电子知识,一查百通!

已收录词条937245个