LDO稳压器是low dropout regulator,是一种线性稳压器。线性稳压器使用在其线性区域内运行的晶体管或 FET,从应用的输入电压中减去超额的电压,产生经过调节的输出电压。所谓压降电压,是指稳压器将输出电压维持在其额定值上下 100mV 之内所需的输入电压与输出电压差额的最小值。LDO意为低压差线性稳压器,是相对于传统的线性稳压器来说的。传统的线性稳压器,如78xx系列的芯片都要求输入电压要比输出电压高出2v~3V以上,否则就不能正常工作。但是在一些情况下,这样的条件显然是太苛刻了,如5v转3.3v,输入与输出的压差只有1.7v,显然是不满足条件的。针对这种情况,才有了LDO类的电源转换芯片。

Vin >= Vdrop + Vout。

且一般需要两个外接电容:Cin、Cout,一般采用钽电容或MLCC。

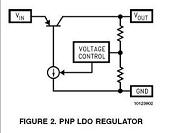

在LDO(Low Dropout)稳压器(图2:LDO稳压器内部结构框图)中,导通管是一个PNP管。LDO的优势就是PNP管只会带来很小的导通压降,满载(Full-load)的跌落电压的典型值小于500mV,轻载(Light loads)时的压降仅有10~20mV。LDO的压差为:

Vdrop = Vsat (LDO 稳压器)

LDO稳压器电路是一种用途极为广泛的集成电路(IC)。

1、电路架构简单

2、输出纹涟漪很低

3、外部组件很少且简单等等。

压差Dropout、噪音Noise、共模/纹波抑制比(PSRR)、静态电流Iq,这是LDO的四大关键数据。

产品设计师按产品负载对电性能的要求结合四大要素来选择LDO。在手机上用的LDO要求尽可能小的噪音(纹波),在没有RF的便携式产品需求静态电流小的LDO。

维库电子通,电子知识,一查百通!

已收录词条937245个