主存储器,英文为Main memory,亦可简称主存,是计算机存储系统的核心,起承上启下的作用。主存储器用来存放计算机运行期间所需要的程序和数据,主要性能指标有存储容量、存取时间、存储周期和存储器带宽。

主存储器,是计算机硬件的一个重要部件,其作用是存放指令和数据,并能由中央处理器(CPU)直接随机存取。现代计算机为了提高性能,兼顾合理的造价,往往采用多级存储体系,即有存储容量小、存取速度高的高速缓冲存储器,存储容量和存取速度适中的主存储器。

主存储器是按地址存放信息的,存取速度一般与地址无关。32位(比特)的地址能表达4GB的存储器地址。这对目前多数应用已经足够,但对于某些特大运算量的应用和特大型数据库显然是不够的,因此提出64位结构的要求。

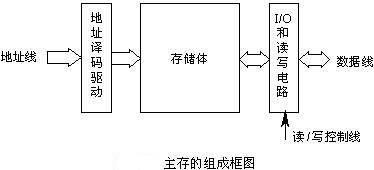

主存储器通常由存储体、地址译码驱动电路、I/O和读写电路等部分组成,其组成的框图如图所示。

其中,存储体是存储单元的集合,用来存放数据;地址译码驱动电路包含译码器和驱动器两部分,译码器将地址总线输入的地址码转换成与之对应的译码输出线上的有效电平,以表示选中了某一存储单元,然后由驱动器提供驱动电流去驱动相应的读写电路,完成对被选中存储单元的读写操作;I/O和读写电路包括读出放大器、写入电路和读写控制电路,用以完成被选中存储单元中各位的读出和写入操作。

1.信息保存的长短分:只读存储器(ROM)与随机存取存储器(RAM)。

2.生产工艺分:静态存储器与动态存储器。

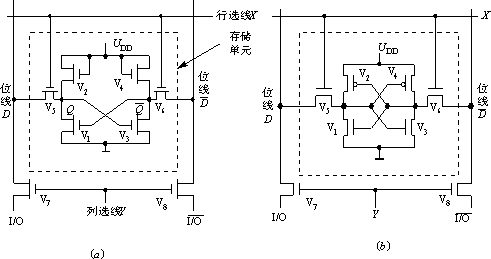

静态存储器

静态存储器(SRAM):读写速度快,生产成本高,多用于容量较小的高速缓冲存储器。

动态存储器(DRAM):读写速度较慢,集成度高,生产成本低,多用于容量较大的主存储器。

主存储器指标有存储速度、存储容量、CL、SPD芯片、奇偶效验、内存带宽等。

1.存储速度

内存的存储速度用存取一次数据的时间来表示,单位为纳秒,记为ns,1秒=10亿纳秒,即1纳秒=10ˉ9秒。Ns值越小,表明存取时间越短,速度就越快。目前,DDR内存的存取时间一般为6ns,而更快的存储器多用在显卡的显存上,如:5ns、 4ns、 3.6ns、 3.3ns、 2.8ns等。

2.存储容量

目前常见的内存存储容量单条为128MB、256MB、512MB,当然也有单条1GB的,内存,不过其价格较高,普通用户少有使用。就目前的行情来看,配机时尽时使用单条256MB以上的内存,不要选用两根128MB的方案。 提示:内存存储容量的换算公式为,1GB=1024MB=1024*1024KB。

3.CL

CL是CAS Lstency的缩写,即CAS延迟时间,是指内存纵向地址脉冲的反应时间,是在一定频率下衡量不同规范内存的重要标志之一。对于PC1600和PC2100的内存来说,其规定的CL应该为2,即他读取数据的延迟时间是两个时钟周期。也就是说他必须在CL=2R 情况下稳寰工作的其工作频率中。

4.SPD芯片

SPD是一个8针256字节的EERROM(可电擦写可编程只读存储器) 芯片,位置一般处在内存条正面的右侧,里面记录了诸如内存的速度、容量、电压与行、列地址、带宽等参数信息。当开机时,计算机的BIOS将自动读取SPD中记录的信息。

5.奇偶校验

奇偶校验就是内存每一个字节外又额外增加了一位作为错误检测之用。当CPU返回读顾储存的数据时,他会再次相加前8位中存储容量的数据,计算结果是否与校验相一致。当CPU发现二者不同时就会自动处理。

6.内存带宽

从内存的功能上来看,我们可以将内存看作是内存控制器(一般位于北桥芯片中)与CPU之间的桥梁或仓库。显然,内存的存储容量决定“仓库”的大小,而内存的带决定“桥梁的宽窄”,两者缺一不可。 提示:内存带宽的确定方式为:B表示带宽、F表于存储器时钟频率、D表示存储器数据总线位数,则带宽B=F*D/8(如常见100MHz的SDRAM内存的带宽=100MHz*64bit/8=800MB/秒、常见133MHz的SDRAM内存的带宽133MHz*64bit/8=1064MB/秒)。

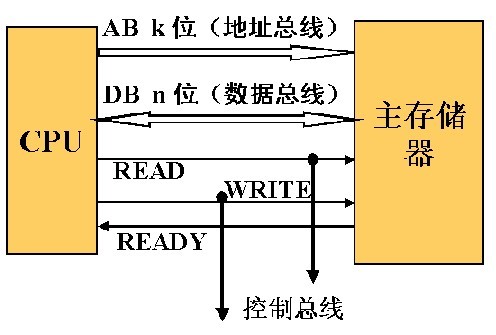

CPU对存储器进行读写操作,首先由地址总线给出地址信号,然后发出读操作或写操作的控制信号,在数据总线上进行信息交流。如果将由若干存储芯片构成的存储器和CPU看做两个黑盒子,通过地址总线(AB)、数据总线(DB)、控制总线(CB)相联的结构如图所示。

主存储器与CPU的连接

存储器地址寄存器(MAR)和存储器数据寄存器(MDR)是主存和CPU之间的接口。MAR可以接受来自程序计数器的指令地址或来自地址形成部件的操作数地址,以确定要访问的单元。MDR是向主存写入数据或从主存读出数据的缓冲部件。MAR和MDR从功能上看属于主存,但在小型计算机、微型计算机中常放在CPU内。

CPU与主存的硬连接是两个部件之间联系的物理基础,具体完成读或写还需要两个部件之间的软连接,即CPU向主存发出的读或写命令,这才是两个部件之间有效工作的关键。读写的基本操作如下:

(1)读。读操作是指从CPU送来的地址所指定的存储单元中取出信息,再送给CPU,其操作过程如下:

① 地址→MAR→AB:CPU将地址信号送至地址总线;

② Read:CPU发出读命令;

③ Wait for MFC:等待存储器工作完成信号;

④ M(MAR)→DB→MDR:读出信息经数据总线送至CPU。

(2)写。写操作是指将要写入的信息存入CPU所指定的存储单元中,其操作过程如下:

① 地址→MAR→AB:CPU将地址信号送至地址总线;

② 数据→MDR→DB:CPU将要写入的数据送至数据总线;

③ Write:CPU发出写命令;

④ Wait for MFC:等待存储器工作完成信号。

由于CPU和主存的速度存在着差距,所以两者之间的速度匹配是很关键的。通常有两种匹配方式:同步存储器读取和异步存储器读取。上面给出的读写基本操作是以异步存储器读取来考虑的,CPU和主存之间没有统一的时钟,由主存工作完成信号(MFC)通知CPU“主存工作已完成”。

从20世纪70年代起,主存储器已逐步采用大规模集成电路构成。最普遍也最经济的是动态随机存储器芯片(DRAM)。1995年集成度为64Mb(可存储400万个汉字)的DRAM芯片开始商业性生产,16MbDRAM芯片已成为市场主流产品。DRAM芯片的存取速度适中,一般为50~70ns。有一些改进型的DRAM,如EDODRAM(即扩充数据输出的DRAM),其性能可较普通DRAM提高10%以上,又如SDRAM(即同步DRAM),其性能又可较EDODRAM提高10%左右。1998年SDRAM的后继产品为SDRAMⅡ(或称DDR,即双倍数据速率)的品种已上市。

动态随机存储器

在追求速度和可靠性的场合,通常采用价格较贵的静态随机存储器芯片(SRAM),其存取速度可以达到了1~15ns。无论主存采用DRAM还是SRAM芯片构成,在断电时存储的信息都会“丢失”,因此计算机设计者应考虑发生这种情况时,设法维持若干毫秒的供电以保存主存中的重要信息,以便供电恢复时计算机能恢复正常运行。鉴于上述情况,在某些应用中主存中存储重要而相对固定的程序和数据的部分采用“非易失性”存储器芯片(如EPROM,快闪存储芯片等)构成;对于完全固定的程序,数据区域甚至采用只读存储器(ROM)芯片构成;主存的这些部分就不怕暂时供电中断,还可以防止病毒侵入。

维库电子通,电子知识,一查百通!

已收录词条937245个