视频控制器就是对视频进行控制的一种设备,一般显卡驱动程序或者DirectX中都自带视频控制器。视频控制器在很多行业中都广泛应用,比如输出视频控制模块有2个时钟域:系统时钟域和显示时钟域。系统时钟频率根据所选用的SDRAM类型而采用固定的166MHz;对于分辨率为1280×720的高清电视来说,显示时钟域可以选用70 MHz 左右的频率。

视频控制器一般由显卡驱动程序或DirectX中自带。

视频控制器模块是芯片与显示平台的数据接口,对检验芯片设计是否成功起着重要的作用,有必要把它单独划分为一个子模块。为了提高设计的成功率,在设计初期采用了基于FPGA的原型验证。整个系统的FPGA原型验证平台分为2个部分,硬件设计和基于RISC CPU的软件解码,两部分协同工作,既可以验证软件和硬件的解码结果,又可以加速整个解码过程。

1、TCP/IP 网络远程图像传输

2、视频编码/解码可选

3、高清晰实时画质D1(720×576)

4、IP数字视频流输入,1-4路模拟视频输出可选

6、模拟视频流输入,1-4路IP数字视频输出

7、亮度、对比度、饱和度、锐度、色调可调

8、可扩展传感器和报警装置(4防区/4继电器输出)

9、占用网络带宽可调

10、报警前后的图像捕捉

11、云台可远程控制(45个品牌)

12、多重密码保护

13、固件可在线升级

14、内置网页服务器

15、支持远程控制

16、移动侦测

17、支持无线LAN

18、数字水印

19、1路双向语音

实现数字图像格式转换与缩放的硬件

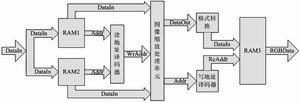

需要实现这个要求,一些硬件等都需要进行适当配置,显示设备采用分辨率为1280×720的高清晰度电视机,输出到高清晰度电视机显示时采用图像中心对齐的方式。当把解码好的数字图像数据送到高清晰度电视显示时,如果不经过图像缩放处理,那么显示屏幕中间放解码好的数字图像,其他的地方用黑色填充。在进行缩放处理时,遵循上面的规律。先把视频控制器输出模块前端按照逐行扫描排列好送来的数据进行数据格式转换,再把RGB不为零(即不为黑色)的像素数据按每帧和逐行扫描规律轮流放到两块同样大小的片内缓存RAM中。

其工作方式也很重要,读取RAM1或RAM2中数据的地址后,可以通过地址译码器得到该点像素值的行列地址,即得到m、n的值。把m、n值送到图像缩放处理单元,通过缩放处理得到新的图像数据和新的图像数据地址,再通过写地址译码器得到在输出RAM3中按照逐行扫描格式输出的地址,该地址用来存放格式转换后的数据。,从存储转换数据的RAM3中可以直接输出显示所需要的RGB数据。

一、视频控制模块原理框图及功能分析

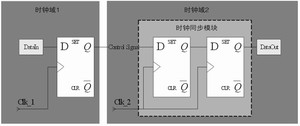

输出视频控制模块的结构框图如图1所示,有2个时钟域:系统时钟域和显示时钟域。

系统时钟域含有2个对外接口:系统接口,主要包含上层系统发出的指令以及输出控制模块的反馈信息;DRAM接口,包含数据专用总线为输出控制模块提供的信号,用来于向DRAM请求显示的图像数据。

系统时钟域中的显示输入控制子模块(Disp In Ctrl)首先用于接收系统传来的StartDisp和EndDisp信号,来启动或关闭视频数据的输出显示功能,同时发出帧图像显示完毕信号(FrameDone),通知系统更换下一副图像的地址信息(ImageAddress);其次,它用于向DRAM发出请求,通过专用数据通道读取需要显示的图像数据;它还要控制输入多路选择模块(Input MUX),从而完成向片内SRAM写数据的任务;,该模块要与显示时钟域的信息交互,向时钟域同步模块(Clk Domain Sync)发送显示使能信号(DispEn Sys),控制图像显示的开启和关闭。系统时钟域的另一个子模块——输入多路选择模块会按照一定的规律选择片内双口SRAM,控制存储器地址,完成向存储器写入显示图像数据的任务。

显示时钟域含有一个对外显示设备接口,主要包含用于显示的控制信号和已完成转换的数据信息。显示时钟域包含2个子模块,一个是输出多路选择子模块(Output MUX),用于实现对双口SRAM的选择和地址控制,按照一定的规律读取要显示的图像数据;还要进行数据的打包。另外一个子模块是显示输出控制模块(Disp Out Ctrl),用于实现对TV编码器的控制、YUV信号向RGB信号的转换以及对数字图像的缩放,信号包括显示时钟、行同步、帧同步以及RGB图像数据等;它还要控制输出多路选择模块以读取显示数据;,它要与系统时钟域进行交互, 配合数据在两个时钟域之间的传递。

二、视频控制模块采用的特殊技术

时钟域同步模块是输出控制模块设计的重点,它主要负责两个时钟域之间的控制信号传递。跨时钟域的信号传递设计较为麻烦, 所以设计中将传递的信号分为两类:数据信号和控制信号,其中控制信号就是通过时钟域同步模块传递。对需要跨时钟域传递的信号数进行精简,在方案中只需要2个信号:WrDone信号由系统时钟域发出,通知显示时钟域某块双口SRAM中的数据已经更新完毕,可以读取并进行显示输出;RdDone信号由显示时钟域发出,通知系统时钟域某块双口SRAM中的数据已经显示完毕,可以更新其内部的数据。信号在不同的时钟域之间传递需要采取消除亚稳态(Metastability)的处理措施,可使信号通过两级寄存器锁存输出,如图2所示。

图2 跨时钟域信号亚稳态消除电路

图3 视频输出子模块的硬件实现框图

设计中有两点值得注意,首先,时钟域同步电路应放在一个独立的模块中,保证综合工具的优化、时序分析的正确,并方便电路的分析和调试;同时,为了能够使信号的目标时钟域采集到信号变化,设计中传递的控制信号都采用电平信号表征。

维库电子通,电子知识,一查百通!

已收录词条937245个