语音编解码器采用鲁棒的先进低复杂性波形插入技术,提供超低位速率下长话级音质性能,且具有FEC(前向纠错)、SDD(软决策解码)、DTX(非连续发送检测)、VAD(语音激活检测)、CNG(舒适噪声发生)、STD和DTMF信号检测功能。因此,该语音编解码器可广泛用于语音存储和回放、VoIP、数字PMR/LMR、再生数字语音中继等领域。

长话级音质鲁棒先进的低复杂性波形插入编码算法:多种压缩速率模式则为2 050 b/s,2 400 b/s、2 750 b/s或3 600 b/s(带FEC功能);集成16位A/D和D/A转换器、模拟增益放大器和数字低通滤波器:数据包压缩时间长度分20 ms,40 ms,60 ms和80 ms;具有VAD、CNG、STD和DTMF功能;+1.8 V和+3.3 V双电源供电:采用48引脚LQFP(L4)和48引脚VQFN(Q3)封装;工作温度范围为-40℃~+85℃。

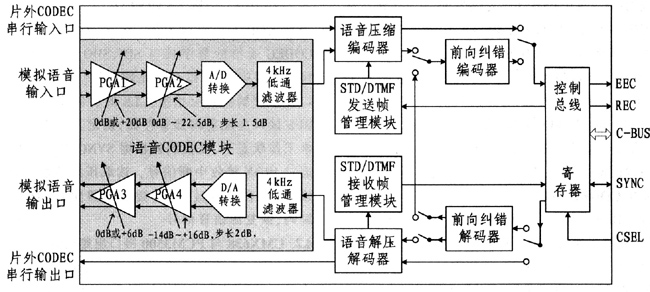

语音编解码器的内部结构包括模拟和数字两部分,加图所示。当端口CSEL输入低电平时,即选择使用外部语音解码器(CODEC),可通过串行接口SSP 与外部器件交换数据,编码器和解码器选择片外CODEC的数据通道,端口EEC和REC输出分别使能和复位片外的CODEC;当CSEL输入高电平时,CMX638选用内部CODEC模块,该模块包括输入/输出通道的可编程增益放大器(PGA),16位PCM A/D和D/A转换器以及通带频率为4 kHz的低通滤波器,可有效实现模拟信号转换成数字信号及数字信号转换成模拟信号的过程。

主机通过控制总线C-BUS接口配置内部寄存器,实现不同功能;端口SYNC使主机与CMX638同步;语音压缩编码器将源信号压缩成低比特率的数据帧,解码器把数据帧解压缩,恢复源信号;如果使用FEC功能,开关则选择前向纠错编码器和解码器,两者加入到数据的压缩和解压缩过程中:STD/DTMF管理模块提供语音信号的特殊处理功能,实现单音或双音检测,提高语音压缩和解压质量。

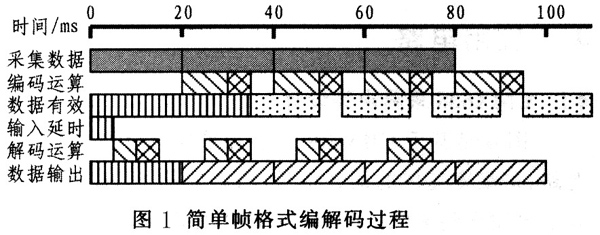

1 不带FEC的简单帧格式编解码

语音编解码器提供简单的编解码数据帧格式,其压缩速率包括2 050 b/s,2 400 b/s,2 750 b/s,此过程不带FEC,STD和DTMF功能。CMX638每隔20 ms采集160个16位数据(A/D转换器的采样率为8 kHz),当个20 ms结束后,开始编码运算,由于信号的异同会产生不同抖动延时,主机在40 ms的时刻读取帧数据。以后每隔20 ms操作一次,形成流水线作业。在解码过程中,在0 ms时刻主机向CMX638输入一帧数据后,CMX638开始解码运算,与编码相似也会出现算法抖动延时,个样本的输出时刻由内部寄存器IDD决定,其延时应确保输出连续有效的数据。图1为语音编解码器简单帧格式编解码过程。

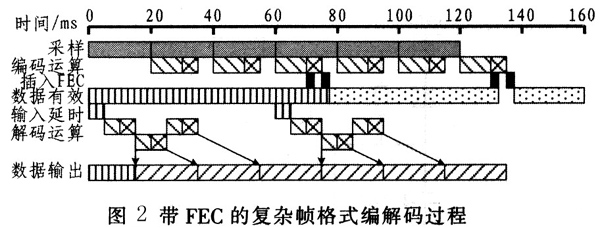

2 带FEC的复杂帧格式编解码

语音编解码器可提供带前向纠错的编解码数据帧格式,其数据包长度为60 ms,包括3帧数据,其压缩速率为3 600 b/s。语音编解码器在0时刻开始采样,每隔20 ms进行编码运算,会出现抖动延时,每隔60 ms插入一次FEC编码(图2黑色部分),在80 ms时刻一个数据包稳定有效,主机读出数据,以后每隔60 ms操作一次。在解码过程中,主机向CMX638输入数据包后,开始对每一帧数据解码运算,并会出现抖动延时,设置适当的内部寄存器IDD,可在延时后输出连续有效的数据。图2是带FEC的复发帧格式编解码过程,其数据包压缩时间为60 ms。

2.1 数据帧格式

语音编解码器编码后输出的数据帧格式较简单,无帧头和其他控制标志信息,直接输出有效数据。当压缩速率为2 050b/s时,每隔20 ms产生一帧数据,有效数据位为41 bit,占用6字节,主机必须以字节为单位与CMX638交换数据,所以应该输入/输出6字节,其中字节先进先出,7个无效比特位不影响编解码。当压缩速率为2 400 b/s时,其工作原理与2 050 b/s压缩速率相同,有效数据为48 bit,恰好占用6字节,无无效比特位。当压缩速率为2 750 b/s,有效数据为55bit,占用7字节,1个无效比特位,必须输入/输出7字节。当压缩速率为3 600 b/s,带FEC功能,每隔60 ms产生包括3帧的数据包,有效数据为216 bit,采用硬比特格式,占用27字节。而采用软比特格式时,则占用108字节。

3 主机与片外CODEC接口

主机通过C-BUS串行接口与CMX638交换数据。写操作时,CSN为低,先写入要访问的寄存器地址,再写入有效数据,以字节为单位,结束时CSN拉高;读操作时,先写入地址,接着读取数据。在CLK上升沿采样,时钟频率为5 MHz;每两次CSN操作应至少相隔1μs。

当语音编解码器选用外部CODEC时,利用SSP接口与外部CODEC交换数据。当STRB同步脉冲到达,如果是写操作,SDI输入16 bit数据;如果是读操作,SDO输出16 bit数据。SCLK的时钟频率为6.6 MHz,时钟沿采样输入数据方式取决于内部寄存器EXCODECCONT($0B)。

维库电子通,电子知识,一查百通!

已收录词条937245个