SDRAM全称为Synchronous Dynamic Random Access Memory,即同步动态随机存储器。尽管它也是动态存储器,信息也是存放在电容上的,也常要定时刷新,甚至它也有行选通RAS、列选通信号CAS,地址信号线也是复用的,但它在内部结构及使用上又与标准DRAM有很大不同。引起不同的基本出发点就是希望SDRAM的速度更快一些,满足PC机对内存速度的要求。

(1) 容量。SDRAM的容量经常用XX存储单元×X体×每个存储单元的位数来表示。例如某SDRAM芯片的容量为4M×4×8bit,表明该存储器芯片的容量为16 M字节。或128 M bit。

(2) 时钟周期。它代表SDRAM所能运行的频率。显然,这个数字越小说明SDRAM芯片所能运行的频率就越高。

对于一片普通的PC-100 SDRAM来说,它芯片上的标识10代表了它的运行时钟周期为10 ns,即可以在100 MHz的外频下正常工作。例如芯片上标有7.5,表示它可以运行在133MHz的频率上。

(3) 存取时间。目前大多数SDRAM芯片的存取时间为5、6、7、8或10 ns,但这可不同于系统时钟频率。比如芯片厂家给出的存取时间为7 ns而不是存取周期。因此,它的系统时钟周期要长一些,例如10 ns,即外频为100 MHz。

(4) CAS的延迟时间。这是列地址脉冲的反应时间。现在大多数的SDRAM(当外频为100 MHz时)都能运行在CASLatency(CL)=2或3的模式下,也就是说,这时它们读取数据的延迟时间可以是两个时钟周期也可以是三个时钟周期。在SDRAM的制造过程中,可以将这个特性写入SDRAM的EEPROM中,在开机时主板的BIOS就会检查此项内容,并以CL=2这一默认的模式运行。

(5) 综合性能的评价。对于PC 100内存来说,就是要求当CL=3的时候,tCK(时钟周期) 的数值要小于10 ns,tAC要小于6 ns。至于为什么要强调是CL=3的时候呢,这是因为对于同一个内存条,当设置不同CL数值时,tCK的值很可能是不相同的,当然tAC的值也是不太可能相同的。总延迟时间的计算公式一般为:

总延迟时间=系统时钟周期×CL模式数+存取时间例如,某PC100内存的存取时间为6 ns,我们设定CL模式数为2(即CAS Latency=2),则总延迟时间=10 ns×2+6 ns=26 ns。这就是评价内存性能高低的重要数值。

SDRAM与标准DRAM的主要不同表现在:

(1) 异步与同步。前面介绍的标准DRAM是异步DRAM,也就是说对它读/写的时钟与CPU的时钟是不一样的。而在SDRAM工作时,其读/写过程是与CPU时钟(PC机中是由北桥提供的)严格同步的。

(2) 内部组织结构。SDRAM芯片的内部存储单元在组织上与标准DRAM有很大的不同。在SDRAM内部一般要将存储芯片的存储单元分成两个以上的体(bank)。最少两个,目前一般做到4个。这样一来,当对SDRAM进行读/写时,选中的一个体(bank)在进行读/写时,另外没有被选中的体(bank)便可以预充电,做必要的准备工作。当下一个时钟周期选中它读或写时,它可以立即响应,不必再做准备。这显然能够提高SDRAM的读/写速度。而标准DRAM 在读/写时,当一个读/写周期结束后,RAS和CAS都必须停止激活,然后要有一个短暂的预充电期才能进入到下一次的读/写周期中,其速度显然会很慢。标准的DRAM可以看成内部只有一个体的SDRAM。

为了实现内部的多体并使它们能有效地工作,SDRAM就需要增加对于多个体的管理,这样就可以控制其中的体(bank)进行预充电,并且在需要使用的时候随时调用。一个具有两个体(bank)的SDRAM一般会多一条叫做BA0的引脚,实现在两个bank之间的选择:一般地,当BA0是低电平时,表示Bank0被选择;而当BA0是高电平时,Bank1就会被选中。显然,若芯片内有4个体(bank)时,就需要两条引线来选择,通常就是BA0和BA1。

(3) 读/写方式。标准的DRAM的读/写都是每读/写一个存储单元,都按照一定的时序,在DRAM规定的读/写周期内完成存储单元的读/写。

这过程与CPU的时钟是异步的,不管CPU用几个时钟周期,只要满足CPU加到芯片上的读/写时间比DRAM所要求的长就可以。

对于SDRAM来说,对它的某一单元的读/写要同CPU时钟严格同步。所以,PC机的北桥芯片组主动地在每个时钟的上升沿给引脚发控制命令。这种情况在下面的时序中可以看到。

除了能够像标准DRAM那样一次只对一个存储单元读/写外,重要的是SDRAM还有突发读/写功能。突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到的存储单元(列)的数量就是突发长度(Burst Lengths,BL)。这种读/写方式在高速缓存Cache、多媒体等许多应用中非常有用。

(4) 智能化。在SDRAM芯片内部设置有模式寄存器,利用命令可对SDRAM的工作模式进行设置。一般标准DRAM只有一种工作模式,无需对其进行设置。

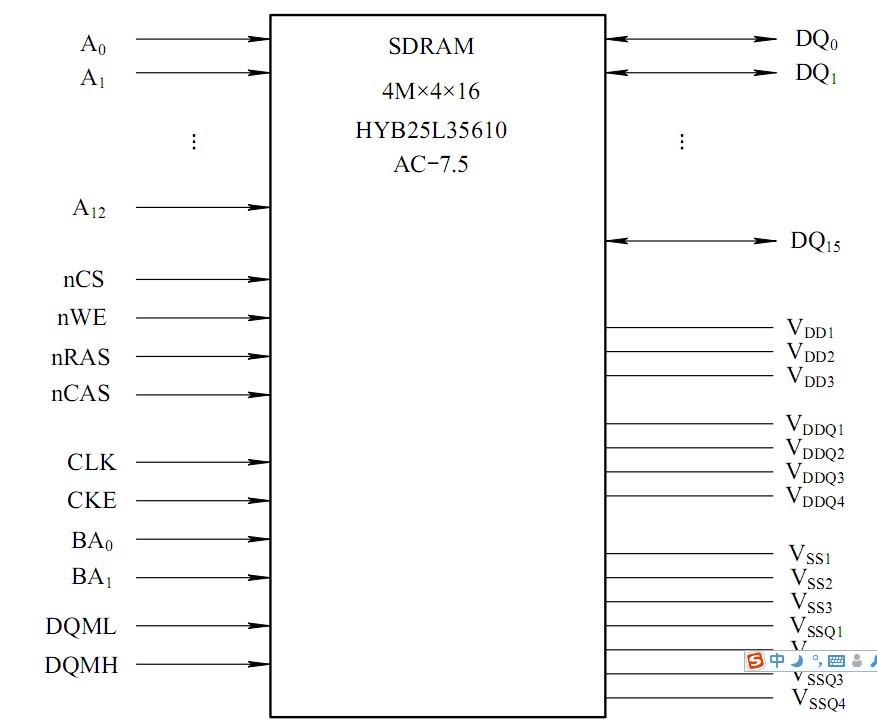

一种典型的SDRAM芯片如图所示。

(1) 引线。图所示的HYB25L35610AC-7.5是一片有54条引线的SDRAM芯片,它的各引线的功能如下:

A0~A12:地址输入引线,当执行ACTIVE命令和READ/WRITE命令时,用来决定使用bank内的哪个基本存储单元。

CLK:时钟信号输入引线。

CKE:时钟允许引线,高电平有效。当这个引脚处于低电平期间,提供给所有bank预充电和刷新的操作。

nCS:片选信号引线,用SDRAM 构成的内存条一般都是多存储芯片架构,这个引脚就用于选择进行存取操作的芯片。

nRAS:行地址选通信号线。

nCAS:列地址选通信号线。

BA0、BA1:bank地址输入信号线。BA信号决定了激活哪一个bank进行读/写或者预充电操作。BA也用于定义Mode寄存器中的相关数据。有两个BA信号就表明芯片内部有4个体。

DQML、DQMH:主要用于屏蔽输入/输出,功能相当于OE(输出允许)信号。它们分别用于屏蔽D0~D7和D8~D15。

VDDQ:DQ供电引脚,可以提高抗干扰强度。

VSSQ:DQ供电接地引脚。

VSS:内存芯片供电接地引脚。

VDD:内存芯片供电引脚,提供+3.3±0.3 V电源

维库电子通,电子知识,一查百通!

已收录词条937245个