数字锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。它由数字鉴相器、数字滤波器与数字压控振荡器(DCO)三个数字电路部件组成。其中数字鉴相器有多种样式,样式不同对环路性能有很大影响。

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得到了广泛的应用。数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还解决了模拟锁相环的直流零点漂移、器件饱和及易受电源和环境温度变化等缺点,此外还具有对离散样值的实时处理能力,已成为锁相技术发展的方向。锁相环是一个相位反馈控制系统,在数字锁相环中,由于误差控制信号是离散的数字信号,而不是模拟电压,因而受控的输出电压的改变是离散的而不是连续的;此外,环路组成部件也全用数字电路实现,故而这种锁相环就称之为全数字锁相环(简称DPLL)。数字锁相环主要由数字鉴相器、可逆计数器、频率切换电路及N分频器四部分组成。数字鉴相器就是DPLL的主要单元。

1. 触发器型数字锁相环(FF—DPLL)

该环路利用一双稳态触发器作数字鉴相器,其状态分别受输入信号与本地受控时钟信号的正向过零点触发,产生的置位与复位脉冲状态变化之间间隔就反映着两信号之间相位误差。

2. 奈奎斯特型数字锁相环(NR—DPLL)

在输入信号进入数字鉴相器之前,先以奈奎斯特速率(固定速率的时钟脉冲)进行抽样,然后再与本地受控时钟信号进行数字相乘,产生数字式相位误差。 ?

3.过零检测式数字锁相环(ZC-DPLL)

环路用本地受控时钟脉冲对输入信号的过零点抽样,非零的实际抽样值大小就反映着相位误差,用该相位误差来调节本地时钟信号的相位。

4.超前滞后型数字锁相环(LL-DPLL)

这种锁相环的鉴相器将逐周地比较输入信号与本地时钟信号的相位,根据相位的超前或滞后输出相应的超前或滞后脉冲,用变换成加脉冲或减脉冲,对应地调节本地时钟相位。

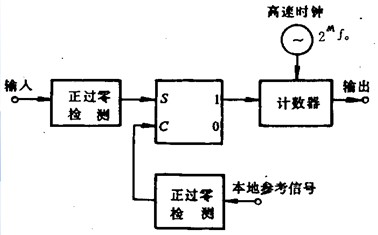

(1)触发器型鉴相器。下图是该型鉴相器的组成示意图。当检测到输入信号正向过零点时,触发器置“1”,而本地参考信号的正向过零点使触发器置“0”复位。

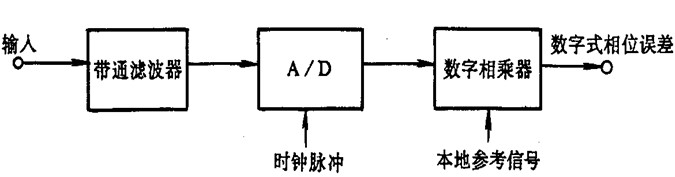

(2) 奈奎斯特速率抽样鉴相器

该型鉴相器组成如下图所示。模数变换器(A/D)的抽样率按带通信号的取样定理选择,以使取样后信号含有充分的输入信号相位信息。

(3) 过零取样鉴相器。

这种鉴相器有两种形式,一种是正过零点取样,这种正过零点取样鉴相器是所有数字鉴相器中最简单的,而且易于实现。另一种则在正负过零点都取样

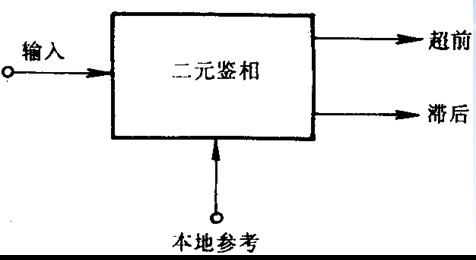

(4)超前滞后取样鉴相器。

下图是用一个简单二元鉴相器表示的这种鉴相器。通过输入信号与本地参考信号(或受控钟脉冲信号)之间比相,形成超前或滞后脉冲输出。超前脉冲意味着本地参考信号相位落后,θe>0,故超前脉冲作用将使本地参考信号相位提前;滞后脉冲表示θe<0,其作用是使本地参考信号相位推后。

维库电子通,电子知识,一查百通!

已收录词条937245个