CPLD (Complex Programmable Logic Device)直译的话称为复杂可编程逻辑芯片。它也属于大规模集成电路LSI (Large Scale Integrated Circuit)里的专用集成电路ASIC (Application Specific Integrated Circuit)。适合控制密集型数字型数字系统设计,其时延控制方便。CPLD是目前集成电路中发展最快的器件之一。

复杂的可编程逻辑器件CPLD规模大,结构复杂,属于大规模集成电路范围。

CPLD有五个主要部分:逻辑阵列块、宏单元、扩展乘积项、可编程连线阵列和I/O控制块。

1.逻辑阵列块(LAB)

一个逻辑阵列块由16个宏单元的阵列组成,多个LAB通过可编程阵列(PIA)和全局总线连接在一起。全局总线从所有的专用输入、I/O引脚和宏单元馈入信号。对于每个LAB有下列输入信号。

来自作为通用逻辑输入的PIA的36个信号

全局控制信号,用于寄存器辅助功能

从I/O引脚到寄存器的直接输入通道

.宏单元

MAX7000系列中的宏单元由3个功能块组成:逻辑阵列、乘积项选择矩阵和可编程寄存器。各部分可以被独自配置为时序逻辑和组合逻辑工作方式。其中逻辑阵列实现组合逻辑,可以为每个宏单元提供5个乘积项。乘积项选择矩阵分配这些乘积项作为到“或门”和“异或门”的主要逻辑输入,以实现组合逻辑函数,或者把这些乘积项作为宏单元中寄存器的辅助输入:如清零、置位、时钟和时钟使能控制。

每个宏单元中的触发器可以单独地编程为具有可编程时钟控制的D、T、JK或RS触发器的工作方式。触发器的时钟、清零输入可以通过编程选择使用专用的全局清零和全局时钟,或使用内部逻辑(乘积项逻辑阵列)产生的时钟和清零。触发器也支持异步清零和异步置位功能,乘积项选择矩阵分配乘积项来控制这些操作。如果不需要触发器,也可以将此触发器旁路,信号直接输给PIA或输出到I/O引脚,以实现组合逻辑工作方式。

3.扩展乘积项

每个宏单元的一个乘积项可以反相回送到逻辑阵列。这个“可共享”的乘积项能够连到同一个LAB中的任何其它乘积项上。尽管大多数逻辑函数能够用每个宏单元中的5个乘积项实现,但在某些复杂的逻辑函数中需要附加乘积项。为提供所需的逻辑资源,可以利用另一个宏单元,MAX70000结构也允许利用共享和并联扩展乘积项,这两种扩展项可作为附加的乘积项直接送到本LAB的任意宏单元中。利用扩展项可保证在实现逻辑综合时,用尽可能少的逻辑资源实现尽可能快的工作速度。

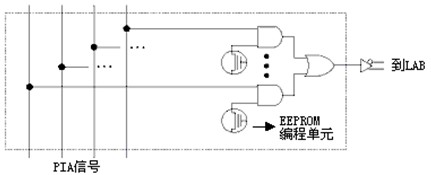

4.可编程连线阵列PIA

通过可编程连线阵列可将各LAB相互连接构成所需的逻辑。这个全局总线是可编程的通道,它能把器件中任何信号源连到其目的地。所有MAX7000系列器件的专用输入、I/O引脚和宏单元输出均馈送到PIA,PIA可把这些信号送到整个器件内的各个地方。只有每个LAB所需的信号才真正给它布置从PIA到该LAB的连线,如图是PIA信号布线到LAB的方式。

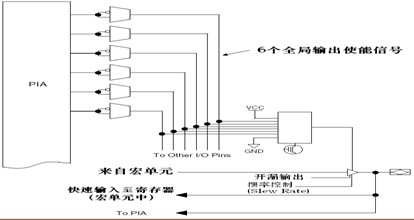

5.I/O控制块

I/O控制块允许每个I/O引脚单独地配置成输入/输出和双向工作方式。所有I/O引脚都有一个三态缓冲器,它能由全局输出使能信号中的一个控制,或者把使能端直接连接到地(GND)或电源(VCC)上。MAX7000系列器件的I/O控制框图如图所示。MAX7000器件有6个全局输出使能信号,它们可以由以下信号驱动:两个输出使能信号、一个I/O引脚的集合、一个I/O宏单元的集合,或者是它“反相”后的信号。

当三态缓冲器的控制端接地(GND)时,其输出为高阻态,而且I/O引脚可作为专用输入引脚。当三态缓冲器的控制端接电源(VCC)时,输出使能有效。

MAX7000结构提供了双I/O反馈,且宏单元和引脚的反馈是相互独立的。当I/O引脚配置成输入时,有关的宏单元可以用于隐含逻辑。

由于CPLD器件厂商众多,CPLD器件的选择同其它通用逻辑器件不同,除考虑器件本身的性能外,配套软件的支持也是器件选择的重要依据。目前市场上已有的CPLD/FPGA器件生产厂家有20多个,而设计软件除生产厂家自行研制的软件外还有几十多种独立软件。加上高性能器件的价格已经不菲,更不用说设计软件的价格,所以如何选用合适的CPLD器件,不只是一件一次性的工作,还涉及到设计软件的选用以及今后进一步工作的开展。

首先,用户应该根据自身的技术环境、技术条件、使用习惯等选择一种合适的软件工具,同时要兼顾EDA技术的发展。与占据优势的软件供应商同时也与多数芯片制造商建立了良好的合作伙伴关系,所以,拥有一种设计软件,再进一步选择不同的工具库,或增加部分配置,即可对不同厂家的不同种类的FPGA产品进行设计。

其次,用户可根据设计的需要确定选择哪一类可编程器件。如果用于航天、军事领域等性能要求高的领域,反熔丝技术的一次编程型可编程芯片是;如果要完成多种算术运算,或是要求在较高速度下,CPLD /FPGA是较好的选择;而对于功能复杂的时序逻辑电路而言,标准门阵列单元型的FPGA具有集成度高、保持灵活和功耗低的优点。

当然,这只是通用准则,关键是所选择的器件能满足设计要求的所有功能,在此基础上,再利用上述准则确定具体的一种器件。

,选定某一厂家的产品,生产同类器件的厂家很多,一般依据以下准则进行选择。

选择有设计软件支持的厂家的芯片,这样可减少资本投入,降低成本。

选择产品设计性能改进有余量的。如果所选择的芯片是某一厂家产品中容量,或是速度的,那么,一但设计需要改进,则有可能在该厂家的芯片中再选不出合适的来了。

设计应用的延续性和可扩展性。如果所选厂家的产品具有很大的局限性,则有可能仅仅适用于很少一部分设计,从而造成设计软件投入上的浪费。

选择性能价格比的。尽管象Xilinx、Altera这样的器件生产厂家都在通过降价来作市场宣传,大多数芯片的价格还是比较高的,所有在满足上述准则的情况下适当考虑价格也是有必要的。

CPLD以及FPGA等相关可编程器件的发展非常快,上面的选择依据是从市场的角度出发对市场份额较大、行业内目前处于地位的部分厂家进行的,具有一定的代表性,但不是十分全面。只有不断跟踪这一领域的技术发展和市场动态才能对可编程芯片有更加全面、不断更新的认识,在应用系统的设计中更好地利用CPLD,以提高产品的设计水平。

目前市场上CPLD的软件种类繁多,软件可以分为厂家集成开发软件、编辑软件,逻辑综合软件、仿真软件及其他测试工具软件等。其中集成开发软件一般是由厂家直接提供,集成了编辑、综合、仿真、布线等功能。其他专门软件属于单项功能的专用软件。

1.集成开发软件

目前CPLD集成开发软件主要有三家公司的软件,分别是Altera公司、Xilinx公司、Lattice公司。

Altera公司提供的开发软件是用户最常用的。此类软件是集成的CPLD开发环境。有多个版本,早期的Max+plusII,MaxplusII Baseline Altera,MaxplusII E+MAX等,基本都可以完成所有的设计输入(原理图或HDL),仿真,综合,布线,下载等工作。而且是免费PLD开发软件,目前Altera公司转向QuartusII软件平台,QuartusII属于新一代PLD开发软件,适合大规模FPGA的开发。

Xilinx公司提供的CPLD软件也有多个版本,早期Foundation软件目前已基本不使用,ISE4.1软件是目前Xilinx公司的主流版本软件。Xilinx公司也提供免费的开发软件,分别是WebPACK ISE 和WebFITTER。

Lattice公司提供的开发软件是ispDesignEXPERT的PLD,目前软件改名为ispLEVER。ispLEVER Starter是Lattice公司的免费PLD开发软件,支持600个宏单元以下的Lattice芯片的设计。

为了提高设计效率,优化设计结果,很多厂家提供了各种软件,用以配合PLD/FPGA芯片厂家提供工具进行更高效率的设计,最常见的组合同时使用HDL逻辑综合软件和PLD/FPGA芯片厂家提供的软件。

2.HDL前端输入与系统管理软件

这类软件主要是帮助用户完成HDL文本的编辑和输入工作,提高输入效率,并不是必须的,更多人更习惯使用集成开发软件或者综合/仿真工具中自带的文本编辑器,甚至可以直接使用普通文本编辑器。UltraEdit是其中使用最为广泛的编辑器。

3.HDL逻辑综合软件

这类软件将把HDL语言翻译成最基本的与或非门的连接关系(网表),输出edf文件,导给PLD/FPGA厂家的软件进行试配和布线。为了优化结果,在进行复杂HDL设计时,基本上都会使用这些的逻辑综合软件,而不使用PLD/FPGA厂家的集成开发软件中自带的逻辑综合功能。如Synplicity公司出品提供的Synplify / Synplify Pro软件,使用相当不错。

4.HDL仿真软件

此类软件主要对设计进行校验仿真,包括布线以前的功能仿真(前仿真)和布线以后包含延时的时序仿真(后仿真),对于一些复杂的HDL设计可能需要这些软件的仿真功能。

如Model Tech公司提供的VHDL/VerilogHDL仿真软件,功能强大。

尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点:

①CPLD更适合完成各种算法和组合逻辑,FP GA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富的结构,而CPLD更适合于触发器有限而乘积项丰富的结构。

②CPLD的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而FPGA的分段式布线结构决定了其延迟的不可预测性。

③在编程上FPGA比CPLD具有更大的灵活性。CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FP GA可在逻辑门下编程,而CPLD是在逻辑块下编程。

④FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现。

⑤CPLD比FPGA使用起来更方便。CPLD的编程采用E2PROM或FASTFLASH技术,无需外部存储器芯片,使用简单。而FPGA的编程信息需存放在外部存储器上,使用方法复杂。

⑥CPLD的速度比FPGA快,并且具有较大的时间可预测性。这是由于FPGA是门级编程,并且CLB之间采用分布式互联,而CPLD是逻辑块级编程,并且其逻辑块之间的互联是集总式的。

⑦在编程方式上,CPLD主要是基于E2PROM或FLASH存储器编程,编程次数可达1万次,优点是系统断电时编程信息也不丢失。CPLD又可分为在编程器上编程和在系统编程两类。FPGA大部分是基于SRAM编程,编程信息在系统断电时丢失,每次上电时,需从器件外部将编程数据重新写入SRAM中。其优点是可以编程任意次,可在工作中快速编程,从而实现板级和系统级的动态配置。

⑧CPLD保密性好,FPGA保密性差。

⑨一般情况下,CPLD的功耗要比FPGA大,且集成度越高越明显。

维库电子通,电子知识,一查百通!

已收录词条937245个