计算机中的记忆元件由触发器组成,而触发器只有两个状态。即“0”态和“1”态,所以每条信号线上只能传送一个触发器的信息。如果要在一条信号线上连接多个触发器,而每个触发器可以根据需要与信号线连通或断开,当连通时可以传送“0”或“1”,断开时对信号线上的信息不产生影响,就需要一个特殊的电路加以控制,此电路即为三态输出电路,又称为三态门。

三态门电路的输出结构与普通门电路的输出结构有很大的不同,它在电路中增加了一个输出控制端EN(Enable的缩写)。当EN=1时,对原电路无影响,电路的输出符合原来电路的所有逻辑关系。当EN=0时,电路内部所有的输出将处于一种关断状态。

可以用一个受EN控制的开关对三态门电路的输出结构进行等效。图2是一个具有三态输出的“非”门的逻辑符号及其等效电路.当EN=1时,非门输出端的开关接通,所以它符合非门的所有逻辑关系。当EN=0时,开关断开,此时在电路的外部看电路输出端的电流几乎为0,所以这是一种高阻状态。

这样,这个电路的输出就有了3个逻辑状态:逻辑0、逻辑1和高阻态。

当多个三态门的输出端连在一起形成总线时,只要保证任何一个时刻只有一个三态门的输出控制端有效,就不会发生总线冲突现象。此时总线上的逻辑电平由那个输出有效的电路确定。

由于三态门通常总是用来驱动总线,所以大部分三态门的输出电流能力要比同系列的普通逻辑门电路强的多。在计算机等其他设备中,总线的位数常常是8的倍数,所以也常常将8个、16个甚至32个三态门的输出控制端连接在一起,形成一个公共控制端。

电路分析:当E为高电位时,经非门后加到两个或非门输入端的均为低电位,此时若A为高电位,则G2为低电位,NMOS管T2断开,G2反馈到上一个或非门后,G1为高电位,NMOS管T1导通,即B与+5 V接通,B点为高电位,B=1;若A为低电位,则G2为高电位,G1为低电位,NMOS管T1断开,T2导通,即B与地接通,B点为低电位,B=0。故此可知,当E=1时:若A=1,则B=1;若A=0,则B=0。

当E为低电位时,经非门后加到两个或非门输入端的均为高电位,终或非门后,G1,G2均为低电位,NMOS管T1与T2均断开,A和B不相通,呈现出高阻状态。

由此可知,此电路有3个状态:

a.E=0,A和B不通,呈高阻态。

b.E=1,A=1时,B=1。

c.E=1,A=0时,B=0。

作用

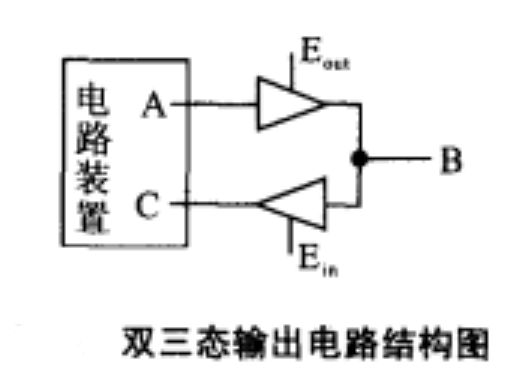

当某元件有双向输出时,可由两个三态门来控制,一个控制输出,一个控制输入。

结构

①双三态输出电路结构如图所示。

②电路分析。

图中A为输出端,C为输入端。当Eout=1,Ein=0时,此电路的传输方向为A→B,即B=A;而当Eout=0,Ein=1时,此电路的传输方向为B→C,即C=B。

维库电子通,电子知识,一查百通!

已收录词条937245个