异或门电路即,有2个输入端、1个输出端。当2个输入端中只有一个是高电平时,输出则为高电平;当输入端都是低电平或都是高电平时,输出才是低电平。

“异或”XOR 函数当有奇数个输入变量为真时,输出为真!

当输入X=0,Y=0 时 输出S=0

当输入X=0,Y=1 时 输出S=1

0代表假 1代表真

异或门主要用在数字电路的控制中!

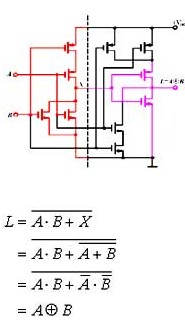

异或运算及异或门由逻辑非、逻辑与和逻辑或可以实现异或逻辑运算,即 。式中“ ”为异或逻辑运算符号,读为“异或”。实现异或运算的门电路是异或门,异或门的真值表如表1.13所示,其逻辑符号如图1.11所示。

二输入异或逻辑的运算规则是:若两个输入变量的逻辑值相同,则它们的异或值为“0”;

若两个输入变量的逻辑值不相同,则它们的异或值为“1”。简言之,“相同则0,相异则1”。

1、电路结构是两寄存器中间夹着组合逻辑,这样可以剔除组合逻辑的毛刺。但是仔细想一想觉得有点可怕,可能有时钟恰好采到毛刺的情况吗?在现实中都是按照时钟来给出数据的,经过组合电路后有了组合电路的延迟,可能使得寄存器的建立保持时间不足,产生亚稳态问题吗?

例如,时钟控制的两个输入通过异或门后结果再被触发器锁存,锁存器的时钟同输入的时钟。

2、对上面例子中的情况异或门产生的毛刺应该采取什么办法清除?

维库电子通,电子知识,一查百通!

已收录词条937245个