根据代码中全部位数相加的“和”来进行奇校验或偶校验。

“和”操作的特点:偶数个1,它的和总是0;奇数个1,它的和总是1。

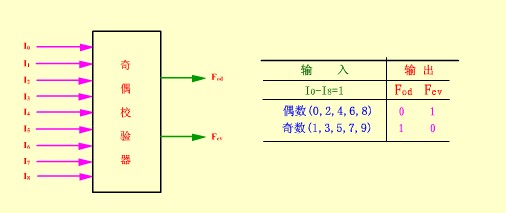

图中所示为一个具有奇校验器的数据传输系统,它采用了两片74LS280:

在发送端:使用一个74LS280产生监督位Fod信号,I8 =1,Fod则指示8位数据1的个数为偶数:

Fod =(I0⊕I1⊕I2⊕I3⊕I4⊕I5⊕I6⊕I7)⊕I8

因此Fod取值使9位码组(8位数据加Fod)中奇数个1

在接收端:9位码组作为第二个74LS280输入,取Fev指示正确性(9位码组保持奇数个1)

Fev =Fod=(I0⊕I1⊕I2⊕I3⊕I4⊕I5⊕I6⊕I7)⊕I8

若Fev =0,则传输正确

组合逻辑电路是由各种门电路组合而成的逻辑电路。该电路的输出只与当时的输入状态有关,而与电路过去的输入状态无关。组合逻辑分析,就是根据给定的逻辑电路图找出输出函数与输入变量之间的逻辑关系。通常的方法是:写出整个电路的输出函数逻辑表达式,或从逻辑表达式进一步求出函数值,列出真值表。

组合逻辑设计,就是根据逻辑功能的要求,得到实现该功能的逻辑电路。工程上的逻辑设计,往往不能用一个或几个简单指标来描述,而要考虑应用的特殊要求。随着中大规模集成电路和可编程逻辑器件的出现和成本的降低,追求最少门数将不再成为设计指标,而转为追求集成块数的减少。

常用的标准组合逻辑构件有数据选择器、数据分配器、译码器、编码器、数码比较器、加法器、奇偶校验器等。它们不仅是计算机中的基本逻辑功能构件,而且也常常应用于其他数字系统中。在高密度可编程逻辑器件出现后,它们又成为软件工具库中的标准元件以供调用,因此必须掌握它们的逻辑结构和功能。

维库电子通,电子知识,一查百通!

已收录词条937245个