时间:2023/7/18 18:51:25

时间:2023/7/18 18:51:25

阅读:456

阅读:456

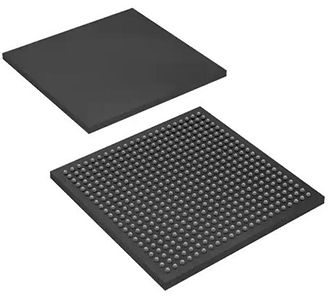

产品型号 | XC3SD1800A-4CSG484I |

描述 | 集成电路FPGA 309 I / O 484CSBGA |

分类 | 集成电路(IC),嵌入式-FPGA(现场可编程门阵列) |

制造商 | Xilinx公司 |

系列 | Spartan?-3ADSP |

打包 | 托盘 |

零件状态 | 活性 |

电压-电源 | 1.14V?1.26V |

工作温度 | -40°C?100°C(TJ) |

包装/箱 | 484-FBGA,CSPBGA |

供应商设备包装 | 484-CSPBGA(19x19) |

基本零件号 | XC3SD1800A |

XC3SD1800A-4CSG484I

制造商包装说明 | 无铅CSBGA-484 |

符合REACH | 是 |

符合欧盟RoHS | 是 |

状态 | 活性 |

可编程逻辑类型 | 现场可编程门阵列 |

最大时钟频率 | 250.0兆赫 |

JESD-30代码 | S-PBGA-B484 |

JESD-609代码 | e1 |

总RAM位 | 1548288 |

CLB数量 | 4160.0 |

等效门数 | 1800000.0 |

输入数量 | 309.0 |

逻辑单元数 | 37440.0 |

输出数量 | 249.0 |

端子数 | 484 |

组织 | 4160 CLBS,1800000个门 |

电源电压标称 | 1.2伏 |

最小供电电压 | 1.14伏 |

最大电源电压 | 1.26伏 |

包装主体材料 | 塑料/环氧树脂 |

包装代码 | BGA |

包装等效代码 | BGA484,22X22,32 |

包装形状 | 四方形 |

包装形式 | 网格阵列 |

峰值回流温度(℃) | 260 |

电源 | 1.2,2.5 / 3.3 |

子类别 | 现场可编程门阵列 |

安装类型 | 表面贴装 |

技术 | CMOS |

终端完成 | 锡/银/铜(Sn95.5Ag4.0Cu0.5) |

终端表格 | 球 |

端子间距 | 0.8毫米 |

终端位置 | 底部 |

时间@峰值回流温度-最大(秒) | 30 |

RoHS状态 | 符合ROHS3 |

水分敏感性水平(MSL) | 3(168小时) |

超低成本,高性能DSP解决方案,适合大批量,注重成本的应用

250MHzXtremeDSPDSP48A片

专用18位乘18位乘法器

可用的管线级,在标准-4速度等级下可增强至少250MHz的性能

用于乘法累加(MAC)操作的48位累加器

集成加法器,用于复杂的乘法或乘法加法运算

集成的18位预加法器

可选的级联乘法或MAC

分层SelectRAM?存储器架构

高达2268Kbit的快速块RAM,具有字节写入功能,可用于处理器应用

高达373Kbit的高效分布式RAM

在BlockRAM上注册的输出,在标准-4速度等级下至少以280MHz运行

双量程VCCAUX电源简化了仅3.3V的设计

挂起,休眠模式会降低系统功耗

低功耗选项可降低静态电流

多电压,多标准SelectIO?接口引脚

多达519个I/O引脚或227个差分信号对

LVCMOS,LVTTL,HSTL和SSTL单端I/O

3.3V,2.5V,1.8V,1.5V和1.2V信令

可选输出驱动器,每个引脚最大24mA

QUIETIO标准降低了I/O开关噪声

完全3.3V±10%的兼容性和热插拔兼容性

每个差分I/O622+Mb/s数据传输速率

LVDS,RSDS,mini-LVDS,HSTL/SSTL差分I/O,带有集成的差分终端电阻

增强的双倍数据速率(DDR)支持

DDR/DDR2SDRAM支持最高333Mb/s

完全兼容32/64位,33/66MHzPCI支持

丰富,灵活的逻辑资源

密度高达53712逻辑单元,包括可选的移位寄存器

高效的宽复用器,宽逻辑,快速进位逻辑

IEEE1149.1/1532JTAG编程/调试端口

八个数字时钟管理器(DCM)

消除时钟偏移(延迟锁定环)

频率合成,乘法,除法

高分辨率相移

宽频率范围(5MHz至超过320MHz)

八个低偏斜全局时钟网络,每半个设备八个额外的时钟,以及丰富的低偏斜路由

与行业标准PROM的配置接口

低成本,节省空间的SPI串行闪存PROM

x8或x8/x16BPI并行NORFlashPROM

具有JTAG的低成本Xilinx?平台闪存

唯一的设备DNA标识符,用于设计验证

在FPGA控制下加载多个比特流

配置后CRC检查

MicroBlaze?和PicoBlaze?嵌入式处理器内核

具有无铅选项的BGA和CSP封装

通用封装支持轻松进行密度迁移

提供XA汽车版本

XC3SD1800A-4CSG484I符号

XC3SD1800A-4CSG484I脚印