时间:2024/4/2 15:45:35

时间:2024/4/2 15:45:35

阅读:369

阅读:369

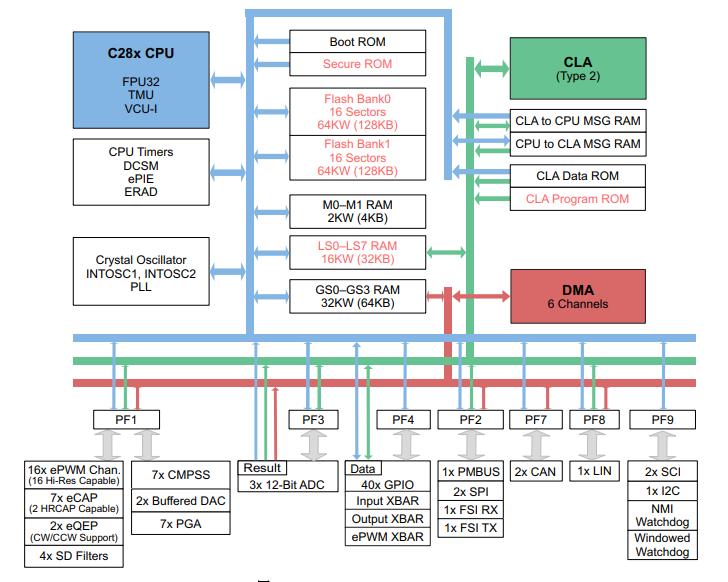

F280049CPMS是一个功能强大的32位浮点微控制器单元(MCU),可让设计人员在单个器件上集成关键的控制外设、差分模拟和非易失性存储器。 实时控制子系统基于TI的32位C28xCPU,可提供100MHz的信号处理性能。C28xCPU的性能通过新的TMU扩展指令集和VCU-I扩展指令集得到了进一步提升,TMU扩展指令集可快速执行包含变换和扭矩环路计算中常见三角运算的算法,VCU-I扩展指令集可降低编码应用中常见复杂数学运算的延迟。CLA允许从C28xCPU上卸载大量的常见任务。CLA是一款与CPU并行执行的独立32位浮点数学加速器。此外,CLA具有其自己的专用存储资源,它可以直接访问典型控制系统中所需的主要外设。与硬件断点和硬件任务切换等主要特性一样,ANSIC子集支持是标准配置。F280049CPMS支持高达256KB(128KW)的闪存,这些闪存分为两个128KB(64KW)存储体,支持并行编程和执行。此外,还以4KB(2KW)和16KB(8KW)块提供高达100KB(50KW)的片上SRAM,以进行高效的系统分区。还支持闪存ECC、SRAMECC/奇偶校验和双重区域安全性。F280049CPMS上集成了高性能模拟块,以进一步支持系统整合。三个独立的12位ADC可准确、高效地管理多个模拟信号,从而最终提高系统吞吐量。模拟前端上的七个PGA可以在转换之前实现片上电压调节。七个模拟比较器模块可以针对跳闸情况对输入电压电平进行持续监控。

●TMS320C28x 32 位 CPU

100MHz

IEEE 754 单精度浮点单元 (FPU)

三角法数学单元 (TMU)

针对常见的三角函数和软件库从 3× 周期提高至 4× 周期

13 周期派克变换

Viterbi/复杂数学单元 (VCU-I)

十个硬件断点(包括 ERAD)

●可编程控制律加速器 (CLA)

100MHz

IEEE 754 单精度浮点指令

独立于主 CPU 执行代码

●片上存储器

在两个独立存储体上提供 256KB (128KW) 的闪存(ECC 保护)

100KB (50KW) RAM(ECC 保护或奇偶校验保护)

支持第三方开发的双区安全

唯一标识 (UID) 号

●时钟和系统控制

两个内部零引脚 10MHz 振荡器

片上晶振振荡器和外部时钟输入

窗口化看门狗计时器模块

丢失时钟检测电路

●1.2V 内核、3.3V I/O 设计

可生成 1.2V 电压的内部 VREG 或直流/直流允许进行单电源设计

欠压复位 (BOR) 电路

| 商品分类 | MCU微控制器 | 品牌 | TI(德州仪器) |

| 封装 | LQFP-64 | 包装 | 整包装 |

F280049CPMS原理图

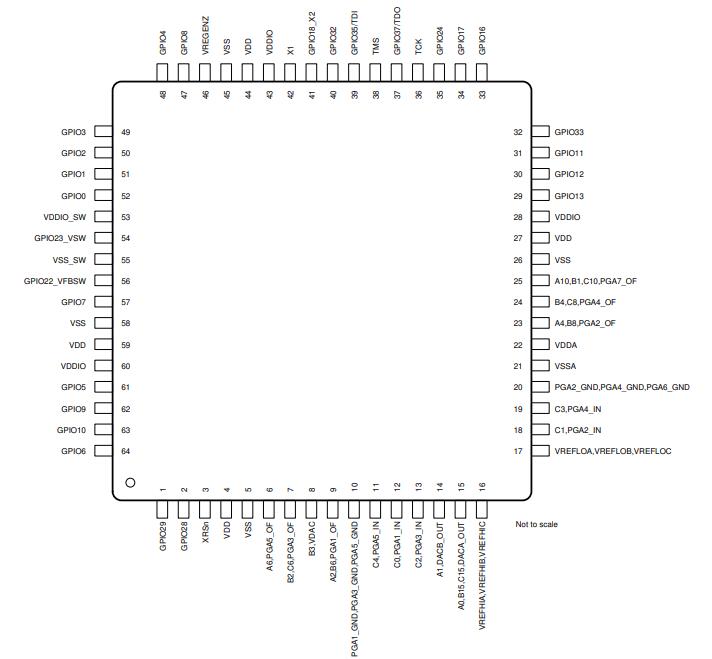

F280049CPMS引脚图

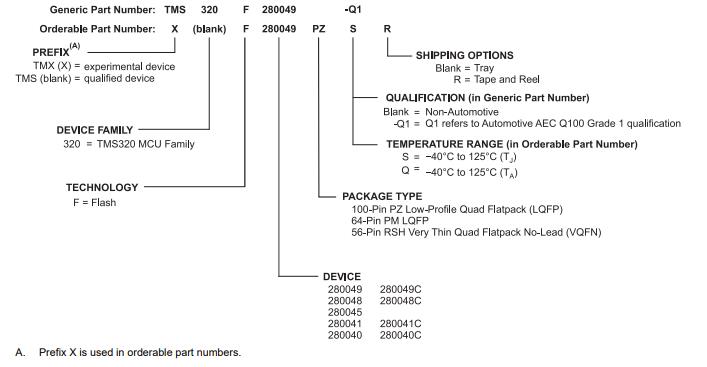

F280049CPMS料号解释