时间:2023/8/1 11:06:45

时间:2023/8/1 11:06:45

阅读:290

阅读:290

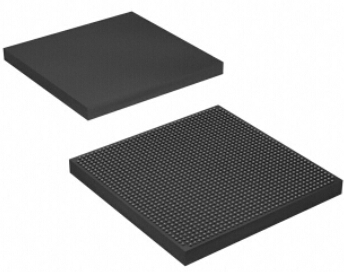

产品型号 | 5SGXEA7K2F40C2N |

描述 | 集成电路FPGA 696 I/O 1517FBGA |

分类 | 集成电路(IC),嵌入式-FPGA(现场可编程门阵列) |

制造商 | 英特尔 |

系列 | Stratix?V GX |

打包 | 托盘 |

零件状态 | 活性 |

电压-电源 | 0.87V?0.93V |

工作温度 | 0°C?85°C(TJ) |

包装/箱 | 1517-BBGA,FCBGA |

供应商设备包装 | 1517-FBGA(40x40) |

基本零件号 | 5SGXEA7 |

5SGXEA7K2F40C2N

可编程逻辑类型 | 现场可编程门阵列 |

符合REACH | 是 |

符合欧盟RoHS | 是 |

状态 | 转入 |

JESD-30代码 | S-PBGA-B1517 |

总RAM位 | 51200000 |

CLB数量 | 23472.0 |

输入数量 | 696.0 |

逻辑单元数 | 622000.0 |

输出数量 | 696.0 |

端子数 | 1517 |

最低工作温度 | 0℃ |

最高工作温度 | 85℃ |

组织 | 23472 CLBS |

电源 | 0.85,1.5,2.5,2.5 / 3,1.2 / 3 |

资格状态 | 不合格 |

座高 | 3.5毫米 |

子类别 | 现场可编程门阵列 |

电源电压标称 | 0.9伏 |

最小供电电压 | 0.87伏 |

最大电源电压 | 0.93伏 |

安装类型 | 表面贴装 |

技术 | CMOS |

温度等级 | 其他 |

终端表格 | 球 |

端子间距 | 1.0毫米 |

终端位置 | 底部 |

长度 | 40.0毫米 |

宽度 | 40.0毫米 |

包装主体材料 | 塑料/环氧树脂 |

包装代码 | BGA |

包装等效代码 | BGA1517,39X39,40 |

包装形状 | 广场 |

包装形式 | 网格阵列 |

制造商包装说明 | FBGA-1517 |

无铅状态/RoHS状态 | 无铅/符合RoHS |

水分敏感性水平(MSL) | 3(168小时) |

技术

28纳米TSMC制程技术

0.85V或0.9V内核电压

低功耗串行收发器

Stratix V GT器件上的28.05-Gbps收发器

用于XFP,SFP +,QSFP,CFP光模块的电子色散补偿(EDC)

自适应线性和决策反馈均衡

发射机预加重和去加重

单个通道的动态重新配置

片上仪器(EyeQ非侵入式数据眼图监控)

背板功能

每秒600兆位(Mbps)到12.5 Gbps的数据速率能力

通用I / O(GPIO)

1.6 Gbps LVDS

1,066-MHz外部存储器接口

片上匹配(OCT)

所有Stratix V器件的1.2V至3.3V接口

嵌入式HardCopy 块

PCIe Gen3,Gen2和Gen1完整协议栈,x1 / x2 / x4 / x8端点和根端口

嵌入式收发器硬核IP

因特拉肯物理编码子层(PCS)

千兆以太网(GbE)和XAUI PCS

10G以太网PCS

串行RapidIO?(SRIO)PCS

通用公共无线电接口(CPRI)PCS

千兆无源光网络(GPON)PCS

电源管理

可编程电源技术

Quartus II集成的PowerPlay功耗分析

高性能芯布

具有四个寄存器的增强型ALM

改进的路由架构减少了拥塞并缩短了编译时间

嵌入式内存块

M20K:20 Kbit,带有硬错误纠正码(ECC)

MLAB:640位

可变精度DSP模块

高达600 MHz的性能

本机支持信号处理,精度从9x9到54x54

新的本机27x27乘法模式

用于脉动有限脉冲响应(FIR)的64位累加器和级联

嵌入式内部系数存储器

预加法器/减法器提高了效率

输出数量的增加允许更多的独立乘法器

小数分频PLL

具有三阶delta-sigma调制的分数模式

整数模式

精确的时钟合成,时钟延迟补偿和零延迟缓冲器(ZDB)

时钟网络

800 MHz架构时钟

全局,象限和外围时钟网络

可以关闭未使用的时钟网络以降低动态功耗

设备配置

串行和并行闪存接口

增强的高级加密标准(AES)设计安全功能

防篡改

部分和动态重新配置

通过协议配置(CvP)

高性能包装

具有相同封装尺寸的多种器件密度实现了不同FPGA密度之间的无缝迁移

FBGA封装,带有封装内的去耦电容器

铅和符合RoHS的无铅选项

HardCopy V迁移

5SGXEA7K2F40C2N符号

5SGXEA7K2F40C2N脚印