时间:2023/7/18 17:56:39

时间:2023/7/18 17:56:39

阅读:475

阅读:475

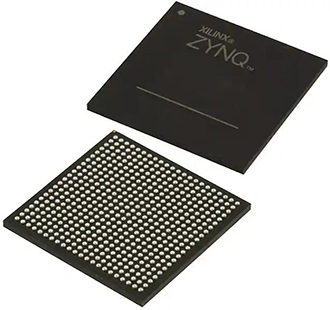

XC7Z015-2CLG485I基于 Xilinx All Programmable SoC架构。这些产品在单个器件中集成了功能丰富的基于双核ARM? Cortex-A9的处理系统(PS)和28nm Xilinx可编程逻辑 (PL)。ARM Cortex-A9 CPU是PS的核心,还包括片上存储器、外部存储器接口和一组丰富的外设连接接口。

产品型号 | XC7Z015-2CLG485I |

描述 | 集成电路SOC CORTEX-A9 766MHZ 485CSBGA |

分类 | 集成电路(IC),嵌入式-片上系统(SoC) |

制造商 | Xilinx公司 |

系列 | Zynq?-7000 |

打包 | 托盘 |

工作温度 | -40°C?100°C(TJ) |

包装/箱 | 484-LFBGA,CSPBGA |

供应商设备包装 | 485-CSBGA(19x19) |

XC7Z015-2CLG485I

制造商包装说明 | BGA-485 |

符合REACH | 是 |

符合欧盟RoHS | 是 |

状态 | 活性 |

地址总线宽度 | 0.0 |

边界扫描 | 是 |

总线兼容性 | CAN,以太网,I2C,PCI,SPI,UART,USB |

最大时钟频率 | 766.0兆赫 |

外部数据总线宽度 | 0.0 |

JESD-30代码 | S-PBGA-B485 |

JESD-609代码 | e1 |

I / O线数 | 4.0 |

端子数 | 485 |

最低工作温度 | -40℃ |

最高工作温度 | 100℃ |

包装主体材料 | 塑料/环氧树脂 |

包装代码 | LFBGA |

包装等效代码 | BGA484,22X22,32 |

包装形状 | 四方形 |

包装形式 | 网格状,低轮廓,精细间距 |

电源 | 1,1.8 |

RAM(字) | 256K |

座高 | 1.6毫米 |

子类别 | 其他微处理器IC |

电源电压标称 | 1.0伏 |

最小供电电压 | 0.95伏 |

最大电源电压 | 1.05伏 |

表面贴装 | 是 |

技术 | CMOS |

温度等级 | 产业 |

终端完成 | 锡/银/铜(Sn / Ag / Cu) |

终端表格 | 球 |

端子间距 | 0.8毫米 |

终端位置 | 底部 |

长度 | 19.0毫米 |

宽度 | 19.0毫米 |

RoHS状态 | 符合ROHS3 |

水分敏感性水平(MSL) | 3(168小时) |

真正的双端口

高达72位宽

可配置为双18Kb

字节奇偶校验支持

片上启动ROM

256KB片上RAM(OCM)

字节奇偶校验支持

多协议动态内存控制器

每个CPU2.5DMIPS/MHz

CPU频率:最高1GHz

一致的多处理器支持

ARMv7-A架构

TrustZone?安全性

Thumb?-2指令集

静态内存接口

定时器和中断

16位模式下的ECC支持

Jazelle?RCT执行环境架构

NEON?媒体处理引擎

两个高速UART(最高1Mb/s)

两个主从I2C接口可编程逻辑

单精度和双精度矢量浮点单元(VFPU)

CoreSight?和程序跟踪宏单元(PTM)

两个兼容SD/SDIO2.0/MMC3.31的控制器

两个全双工SPI端口和三个外围芯片选择

基于双核ARM?Cortex?-A9的应用处理器单元(APU)

32KB1级4路集关联指令和数据高速缓存(每个CPU独立)

512KB8路集关联二级缓存(在CPU之间共享)

DDR3,DDR3L,DDR2或LPDDR2存储器的16位或32位接口

使用8、16或32位宽的单列存储器提供1GB的地址空间

两个USB2.0OTG外围设备,每个外围设备最多支持12个端点

多达54个灵活的多路复用I/O(MIO)用于外围设备引脚分配

支持两个具有IEEEStd802.3和IEEEStd1588版本2.0的10/100/1000三速以太网MAC外设

GPIO具有四个32位存储区,其中PSI/O最多可使用54位(一组32b的存储区和一组22b的存储区),连接到I/O的多达64位(最多2组的32b)可使用GPIO

XC7Z015-2CLG485I封装