时间:2023/7/12 11:37:44

时间:2023/7/12 11:37:44

阅读:1475

阅读:1475

XC2C512-10FT256I具有512宏单元器件专为高性能和低功耗应用而设计。这为高端通信设备带来了节能,为电池供电的设备带来了高速。由于低功耗待机和动态运行,提高了整个系统的可靠性。该设备由通过低功耗高级互连矩阵(AIM)互连的三十二个功能块组成。AIM向每个功能块提供40个真和补输入。功能块由40x56个P项PLA和16个宏单元组成,宏单元包含许多允许组合或注册操作模式的配置位。此外,这些寄存器可以全局复位或预设并配置为D或T触发器或D锁存器。还有多个时钟信号,全局和本地产品术语类型,在每个宏单元的基础上配置。输出引脚配置包括压摆率限制、总线保持、上拉、开漏和可编程接地。

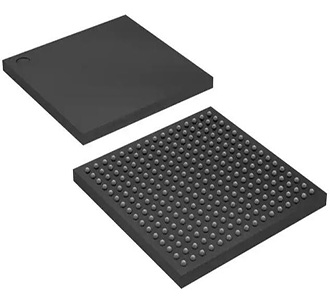

产品型号 | XC2C512-10FT256I |

描述 | 集成电路CPLD 512MC 9.2NS 256BGA |

分类 | 集成电路(IC),嵌入式-CPLD(复杂的可编程逻辑设备) |

制造商 | Xilinx公司 |

系列 | CoolRunner II |

打包 | 托盘 |

工作温度 | -40°C?85°C(TA) |

包装/箱 | 256-LBGA |

供应商设备包装 | 256-FTBGA(17x17) |

基本零件号 | XC2C512 |

XC2C512-10FT256I

制造商包装说明 | 17 X 17 MM,1 MM间距,塑料,FTBGA-256 |

符合REACH | 是 |

状态 | 活性 |

可编程逻辑类型 | 闪存PLD |

系统内可编程 | 是 |

JESD-30代码 | S-PBGA-B256 |

JESD-609代码 | 00 |

JTAG BST | 是 |

专用输入数 | 0.0 |

I / O线数 | 212.0 |

宏单元数 | 512.0 |

端子数 | 256 |

最低工作温度 | -40℃ |

最高工作温度 | 85℃ |

组织 | 0个专用输入,212 I / O |

输出功能 | 宏蜂窝 |

包装主体材料 | 塑料/环氧树脂 |

包装代码 | LBGA |

包装等效代码 | 包装等效代码 |

包装形式 | 网格状,低轮廓 |

峰值回流温度(℃) | 240 |

电源 | 1.5 / 3.3,1.8 |

传播延迟 | 10.0纳秒 |

座高 | 1.55毫米 |

子类别 | 可编程逻辑器件 |

电源电压标称 | 1.8伏 |

最小供电电压 | 1.7伏 |

最大电源电压 | 1.9伏 |

安装类型 | 表面贴装 |

技术 | CMOS |

温度等级 | 产业 |

终端完成 | 锡/铅(Sn63Pb37) |

终端表格 | 球 |

端子间距 | 1.0毫米 |

终端位置 | 底部 |

时间@峰值回流温度-最大值(秒) | 30 |

长度 | 17.0毫米 |

宽度 | 17.0毫米 |

RoHS状态 | 符合RoHS规定 |

水分敏感性水平(MSL) | 3(168小时) |

●针对1.8V系统进行了优化

。高达7.1ns的引脚间延迟

。静态电流低至14μA

●业界最佳的0.18微米CMOSCPLD

。优化的架构可实现有效的逻辑综合

。多电压I/O操作-1.5V至3.3V

●提供多种包装选项

。具有173个用户I/O的208引脚PQFP

。具有212个用户I/O的256球FT(1.0mm)BGA

。具有270个用户I/O的324球FG(1.0mm)BGA

。所有封装均无铅

●先进的系统功能

。系统编程最快·使用IEEE1532(JTAG)接口的1.8VISP

。IEEE1149.1JTAG边界扫描测试

。可选的施密特触发器输入(每个引脚)

。无与伦比的低功耗管理·DataGATE启用信号控制

。四个独立的I/Obank

。RealDigital100%CMOS产品术语生成

。灵活的时钟模式·可选的DualEDGE触发寄存器·时钟分频器(除以2、4、6、8、10、12、14、16)·CoolCLOCK

。具有宏单元控制的全局信号选项·每个宏单元具有相位选择的多个全局时钟·启用多个全局输出·全局设置/复位

。先进的设计安全性

。PLA体系结构·出色的引脚排列保持性·跨功能块100%的产品术语可布线性

。线或和LED驱动器的漏极开路输出选项

。所选I/O引脚上的可选总线保持,三态或弱上拉

。基于未使用的I/O的可选可配置基础

。兼容1.5V,1.8V,2.5V和3.3V逻辑电平的混合I/O电压·SSTL2-1,SSTL3-1和HSTL-1I/O兼容性

。可热插拔

XC2C512-10FT256I符号

XC2C512-10FT256I脚印

型号 | 制造商 | 品名 | 描述 |

XC2C512-7FTG256C | 赛灵思 | CPLD芯片 | 12K Gates 512 Macro Cells 179MHz 0.18um (CMOS) 1.8V 256Pin |

XC2C512-10FTG256I | 赛灵思 | CPLD芯片 | 12K Gates 512 Macro Cells 128MHz 0.18um (CMOS) 1.8V 256Pin |