时间:2023/8/1 11:12:12

时间:2023/8/1 11:12:12

阅读:347

阅读:347

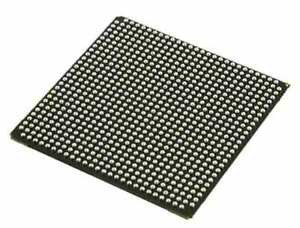

产品型号 | EP2SGX30DF780C5N |

描述 | IC FPGA 361 I/O 780FBGA |

分类 | 集成电路(IC),嵌入式-FPGA(现场可编程门阵列) |

制造商 | 英特尔 |

系列 | Stratix?II GX |

打包 | 托盘 |

零件状态 | 活性 |

电压-电源 | 1.15V?1.25V |

工作温度 | 0°C?85°C(TJ) |

包装/箱 | 780-BBGA |

供应商设备包装 | 780-FBGA(29x29) |

基本零件号 | EP2SGX30 |

EP2SGX30DF780C5N

可编程逻辑类型 | 现场可编程门阵列 |

符合欧盟RoHS | 是 |

状态 | 转入 |

最大时钟频率 | 640.0兆赫 |

CLB-Max的组合延迟 | 5.962纳秒 |

JESD-30代码 | S-PBGA-B780 |

JESD-609代码 | 1号 |

水分敏感性水平 | 3 |

CLB数量 | 33880.0 |

输入数量 | 361.0 |

逻辑单元数 | 33880.0 |

输出数量 | 361.0 |

端子数 | 780 |

最低工作温度 | 0℃ |

最高工作温度 | 85℃ |

组织 | 33880 CLBS |

峰值回流温度(℃) | 245 |

电源 | 1.2,1.2 / 3.3,3.3 |

资格状态 | 不合格 |

座高 | 3.5毫米 |

子类别 | 现场可编程门阵列 |

电源电压标称 | 1.2伏 |

最小供电电压 | 1.15伏 |

最大电源电压 | 1.25伏 |

表面贴装 | 是 |

技术 | CMOS |

温度等级 | 其他 |

终端完成 | 锡/银/铜(Sn / Ag / Cu) |

终端表格 | 球 |

端子间距 | 1.0毫米 |

终端位置 | 底部 |

时间@峰值回流温度最大值(秒) | 40 |

长度 | 29.0毫米 |

宽度 | 29.0毫米 |

包装主体材料 | 塑料/环氧树脂 |

包装代码 | BGA |

包装等效代码 | BGA780,28X28,40 |

包装形状 | 广场 |

包装形式 | 网格阵列 |

制造商包装说明 | 29 X 29 MM,1 MM间距,无铅,MS-034AAM-1,FBGA-780 |

无铅状态/RoHS状态 | 无铅/符合RoHS |

水分敏感性水平(MSL) | 3(168小时) |

■主要设备功能:

TriMatrix存储器由三种RAM块大小组成,可实现真正的双端口存储器和性能高达550 MHz的先进先出(FIFO)缓冲区

最多16个全局时钟网络,每个设备区域最多32个区域时钟网络

高速DSP模块提供乘法器(最高450 MHz),乘法累加功能和有限脉冲响应(FIR)滤波器的专用实现

每个设备最多四个增强的PLL提供扩频,可编程带宽,时钟切换,实时PLL 重配置以及高级乘法和相移

支持多种单端和差分I / O 标准

多达71个通道上的高速源同步差分I / O支持

支持源同步总线标准,包括SPI-4 阶段2(POS-PHY级别4),SFI-4.1,XSBI,UTOPIA IV,NPSI 和CSIX-L1

支持高速外部存储器,包括四数据速率(QDR和QDRII)SRAM,双数据速率(DDR和DDR2)SDRAM和单数据速率(SDR)SDRAM

支持Altera?MegaCore? 功能和Altera Megafunction 合作伙伴计划(AMPPSM)宏功能中的多个知识产权宏功能

使用配置比特流加密支持设计安全性

支持远程配置更新

■收发器模块功能:

具有时钟数据恢复(CDR)的高速串行收发器通道,每个通道提供每秒600兆位(Mbps)到6.375 Gbps 全双工收发器的操作

具有4、8、12、16或20个高速串行收发器通道的设备,可提供高达255 Gbps的串行带宽(全双工)

动态可编程的电压输出差分(VOD)和预加重设置,可改善信号完整性

支持基于CDR的串行协议,包括PCI Express,千兆以太网,SDI,Altera的SerialLite II,XAUI,CEI-6G,CPRI,串行RapidIO,SONET / SDH

动态重新配置收发器通道,以在多种协议和数据速率之间切换

独立的发射器和接收器通道掉电功能,以减少非操作期间的功耗

接收器的自适应均衡(AEQ)功能,以补偿不断变化的链路特性

可选的片上端接电阻(100、120或150Ω),用于改善各种传输介质上的信号完整性

可编程的收发器到FPGA接口,支持8位,10位,16位,20位,32位和40位宽的数据传输

600 和6.335 Gbps的1.2V和1.5V伪电流模式逻辑(PCML)(交流耦合)

信号丢失的接收器指示灯(仅在PIPE 模式下可用)

内置自测(BIST)

热插拔,无需使用外部设备即可支持热插拔或热插拔以及电源排序

速率匹配器,字节重排序,位重排序,模式检测器和字对齐器支持可编程模式

符合PIPE,XAUI和GIGE的专用电路

内置字节排序,以便帧或数据包始终在已知的字节通道中开始

每个收发器模块具有两个PLL输入的发射机,具有独立的时钟分频器,以在其每个发射机上提供不同的时钟速率

8B / 10B编码器和解码器执行8位至10位编码和10位至8位解码

相位补偿FIFO缓冲区在收发器模块和逻辑阵列之间执行时钟域转换

接收器FIFO将接收到的数据与本地参考时钟重新同步

■符合XAUI的通道对齐器

EP2SGX30DF780C5N符号

EP2SGX30DF780C5N脚印