时间:2023/8/1 11:05:40

时间:2023/8/1 11:05:40

阅读:523

阅读:523

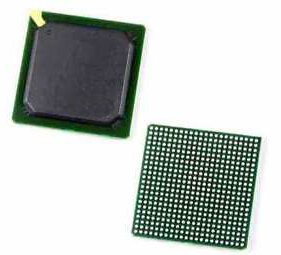

产品型号 | EP2C35F484I8 |

描述 | IC FPGA 322 I/O 484FBGA |

分类 | 集成电路(IC),嵌入式-FPGA(现场可编程门阵列) |

制造商 | 英特尔 |

系列 | Cyclone?II |

打包 | 托盘 |

零件状态 | 活性 |

电压-电源 | 1.15V?1.25V |

工作温度 | -40°C?100°C(TJ) |

包装/箱 | 484-BGA |

供应商设备包装 | 484-FBGA(23x23) |

基本零件号 | EP2C35 |

EP2C35F484I8

可编程逻辑类型 | 现场可编程门阵列 |

状态 | 转入 |

最大时钟频率 | 402.5兆赫 |

JESD-30代码 | S-PBGA-B484 |

JESD-609代码 | 00 |

总RAM位 | 483840 |

CLB数量 | 2076.0 |

输入数量 | 322.0 |

逻辑单元数 | 33216.0 |

输出数量 | 306.0 |

端子数 | 484 |

组织 | 2076 CLBS |

峰值回流温度(℃) | 220 |

电源 | 1.2,1.5 / 3.3,3.3 |

资格状态 | 不合格 |

座高 | 2.6毫米 |

子类别 | 现场可编程门阵列 |

电源电压标称 | 1.2伏 |

最小供电电压 | 1.15伏 |

最大电源电压 | 1.25伏 |

安装类型 | 表面贴装 |

技术 | CMOS |

终端完成 | 锡/铅(Sn63Pb37) |

终端表格 | 球 |

端子间距 | 1.0毫米 |

终端位置 | 底部 |

时间@峰值回流温度最大值(秒) | 20 |

长度 | 23.0毫米 |

宽度 | 23.0毫米 |

附加功能 | 还需要3.3供应 |

包装主体材料 | 塑料/环氧树脂 |

包装代码 | BGA |

包装等效代码 | BGA484,22X22,40 |

包装形状 | 广场 |

包装形式 | 网格阵列 |

制造商包装说明 | FBGA-484 |

无铅状态/RoHS状态 | 包含铅/ RoHS不合规 |

水分敏感性水平(MSL) | 3(168小时) |

■具有4,608至68,416 LE的高密度架构

M4K嵌入式存储块

高达1.1 Mbit的可用RAM,而不会减少可用逻辑

每个块4,096个存储位(每个块4,608个位,包括512个奇偶校验位)

×1,×2,×4,×8,×9,×16,×18,×32和×36的可变端口配置

适用于×1,×2,×4,×8,×9,×16和×18模式的真正双端口(一次读取和一次写入,两次读取或两次写入)操作

字节可在写入期间屏蔽数据输入

最高260MHz的工作频率

■嵌入式乘法器

最多可将150个18×18位乘法器配置为两个独立的9×9位乘法器,性能高达250 MHz

可选的输入和输出寄存器

■高级I / O支持

高速差分I / O标准支持,包括LVDS,RSDS,mini-LVDS,LVPECL,差分HSTL和差分SSTL

单端I / O标准支持,包括2.5 V和1.8 V,SSTL I和II类,1.8 V和1.5 V HSTL I和II类,3.3 V PCI和PCI-X 1.0、3.3- ,2.5V,1.8V和1.5V LVCMOS以及3.3V,2.5V和1.8V LVTTL

外围组件互连特殊利益组(PCI SIG)PCI本地总线规范,修订版3.0符合在32或64位接口上以33或66 MHz运行3.3 V的要求

具有外部TI PHY和Altera PCI Express×1Megacore?功能的PCI Express

133 MHz PCI-X 1.0规格兼容性

高速外部存储器支持,包括DDR,DDR2 和SDR SDRAM,以及QDRII SRAM,Altera IP MegaCore功能的加入为它们提供了易用性

每个I / O元素(IOE)三个专用寄存器:一个输入寄存器,一个输出寄存器和一个输出使能寄存器

可编程总线保持功能

可编程输出驱动强度功能

从引脚到IOE或逻辑阵列的可编程延迟

I / O组分组,用于唯一的VCCIO和/或VREF组设置

MultiVolt?I / O标准支持1.5、1.8、2.5和3.3接口

热插拔操作支持

在配置之前和配置期间,I / O引脚上拉状态较弱的三态

可编程漏极开路输出

系列片上匹配支持

■灵活的时钟管理电路

分层时钟网络,性能高达402.5 MHz

每个设备最多四个PLL提供时钟乘法和除法,相移,可编程占空比和外部时钟输出,从而允许系统级时钟管理和偏斜控制

全局时钟网络中多达16条全局时钟线,驱动整个设备

■设备配置

快速的串行配置允许配置时间少于100毫秒

解压缩功能可减少程序文件的存储并缩短配置时间

支持多种配置模式:主动串行,被动串行和基于JTAG的配置

支持通过低成本串行配置设备进行配置

设备配置支持多种电压(3.3、2.5 或1.8 V)

■知识产权

Altera宏功能和Altera MegaCore功能支持以及Altera宏功能合作伙伴计划(AMPPSM)宏功能支持,适用于广泛的嵌入式处理器,片上和片外接口,外围功能,DSP功能以及通信功能和协议。访问www.altera.com上的Altera IPMegaStore,下载IP MegaCore功能。

Nios II嵌入式处理器支持Cyclone II系列为器件提供了快速上电功能,该功能可加快上电复位(POR)时间。支持快速启动功能的设备在设备订购代码中标有“ A”。例如,EP2C5A,EP2C8A,EP2C15A和EP2C20A。EP2C5A 仅适用于汽车速度等级。EP2C8A和EP2C20A 仅适用于工业速度等级。EP2C15A仅具有快速接通功能,并且可用于商业级和工业级。除了支持更快的POR时间以外,Cyclone II“ A”器件在功能和功能上与非A器件相同。

EP2C35F484I8符号

EP2C35F484I8脚印