G.726是ITU-T定义的一种音频编码算法.主要基于以16-40kibt/s比特率运行的。G.726是ITU前身CCITT于1990年在G.721和G.723标准的基础上提出的关于把64kbps非线性PCM信号转换为40kbps、32kbps、24kbps、16kbps的ADPCM信号的标准。G.726标准算法简单,语音质量高,多次转换后语音质量有保证,能够在低比特率上达到网络等级的话音质量,从而在语音存储和语音传输领域得到广泛应用。

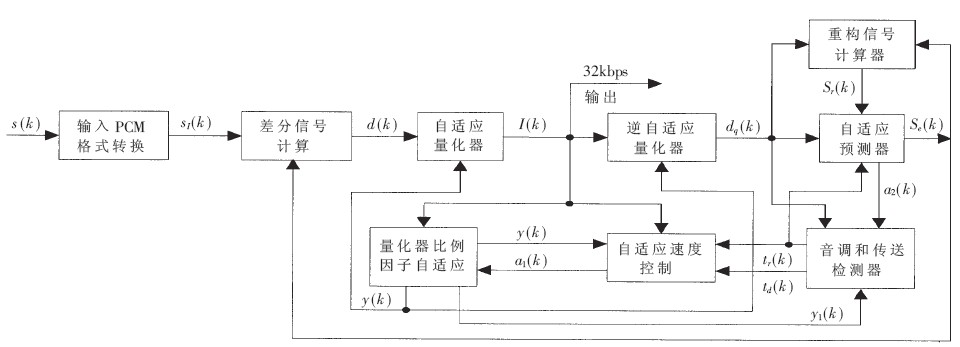

G.726编码器框图如图所示。G.726语音编码器首先将输入的A律或μ律的log-PCM信号S(k)转换成线性的PCM码Sl(k),然后与预测信号Se(k)相减产生差分信号d(k),再对差值信号进行自适应量化,产生2~5比特ADPCM码I(k)。一方面将I(k)送至解码器;另一方面逆自适应量化器利用I(k)产生量化差分信号dq(k)。预测信号Se(k)和量化差分信号dq(k)相加产生本地重构信号Sr(k)。自适应预测器是由二阶极点和六阶零点组成的滤波器,根据重构信号Sr(k)和量化差分信号dq(k)产生输入信号的预测信号Se(k)。量化器比例因子自适应单元根据输入信号的特性计算量化器比例因子y(k),用来控制量化器和逆量化器,以获得自适应功能。量化器比例因子由快速因子和慢速因子两部分,以及速度控制因子al(k)对这两部分的加权组成。速度比例因子al(k)的计算由自适应速度控制单元与音调和传送检测器单元完成。

G.726语音解码器的解码过程实际上已经包含在编码器中,只是多了输出PCM格式转换单元和同步串行编码调整单元。输出PCM格式转换是将线性PCM码转换为A律或μ律PCM码;同步串行编码调整是为了防止多级传输、转换过程中的误差。

设计的编解码器是在语音记录系统中实现G.726建议的速率为32kbps的ADPCM算法,根据实际情况对算法进行了一些简化和改进。

具体简化如下:(1)由于此系统中编解码器的输入信号是线性PCM码,因此PCM码转换模块可以省略。(2)这个算法是用在单纯的语音存储中,可不进行单音/过渡音检测。(3)对量化器比例因子y(k)的更新进行简化。y(k)的更新计算为:

y(k)=al(k)yu(k-1)+[1-al(k)]yl(k-1) (1)

一般情况下,只有语音信号时,al(k)是趋于1的;当输入为平稳信号时,al(k)的值则在0至1之间。对语音存储系统,在输入只有语音的情况下可以粗略地认为al(k)的值近似为1,从而将计算得到的快速比例因子yu(k)直接作为新的比例因子y(k),即y(k)=yu(k-1),降低了算法的复杂度。

利用MATLAB/Simulink和DSP Builder工具进行基于FPGA的DSP设计需要进行一系列的仿真。在Simulink中设计的模型首先要在Simulink中仿真,不仅是验证模型的正确性,而且因为用于ModelSim仿真的TestBench文件中的输入信号激励是由SignalCompiler根据Simulink的仿真结果产生,并且只有仿真后利用SignalCompiler转换产生的VEC文件才有效。在Simulink中完成仿真验证后,使用SignalCompiler将模型进行设计转换。

对于设计转换后产生的VHDL文件,必须进行RTL级仿真。因为Simulink中模型仿真是算法级的,而生成的VHDL描述是RTL级的,两者描述的情况可能不完全符合,因此需要对生成的RTL级VHDL代码进行功能仿真。仿真可通过在ModelSim中运行转换过程所生成的Tcl脚本文件。可以利用转换过程

生成的VEC文件,在Quartus II软件中进行时序仿真。本设计对上述建模的语音编码器完成了仿真,Simulink的仿真结果与ModelSim的仿真结果基本一致,表明两者描述相符合;Quartus II的时序仿真结果表明所设计的语音编码器达到了预期的结果。

维库电子通,电子知识,一查百通!

已收录词条45468个